### THE CATHOLIC UNIVERSITY OF AMERICA

Architecture and Protocol for Optical Packet Switching

A DISSERTATION

Submitted to the Faculty of the

Department of Electrical Engineering and Computer Science

School of Engineering

Of The Catholic University of America

In Partial Fulfillment of the Requirements

For the Degree

Doctor of Philosophy

By

Lesley R.M. Condiff

Washington, D.C.

2011

#### Architecture and Protocol for Optical Packet Switching

Lesley R.M. Condiff Ph.D

#### Director: Mohammad Arozullah

This dissertation proposes a number of single and parallel processor architectures and protocols for optical packet switching in all optical networks making use of a number of recent advances in high speed processors and optical buffers and a number of packet contention resolution techniques in wavelength, time, and space, alternative routing and processing speeds. The input and output lines can transmit multiple wavelengths per line (i.e., wavelength division multiplexed lines). In the developed architectures the header of a packet is separated from the body and is processed for determining the route and wavelength to be used to transmit the packet. The body is delayed for as long as is needed for processing the header. Thus only a portion and not the whole packet need to be saved. This reduces buffer size requirement. The optical packet switch also utilizes dynamically updated Link & Channel Availability Tables and dynamically updated hierarchical Routing Tables (OSPF, Next Best Route). Thirteen different Single Input Processor architectures and the Parallel Input Processor architectures are developed and evaluated with and without packet contention resolution techniques. Parallel processors are used at the output in all architectures except one. The various architectures are simulated by using OPNET software simulation package and their performance is evaluated from these simulation results in terms of packet loss rate, average throughput per line and total throughput. Many of the architectures did not provide acceptable performance. The Parallel Input Processor architecture with the number

of wavelength converters equal to the number of input channels and Parallel Input Processor with Next Best Route are shown to provide the best performance (nearly zero packet loss) when using 10 gigabit per second processors for 10 gigabit per second input line rates. Higher rate input lines can be accommodated by down multiplexing the incoming data into 10 gigabit streams and parallel processing these streams. These results are presented on graphical forms. The results of this dissertation will lead to implementation of optical packet switching with its resultant benefits to the all optical networking. This dissertation by Lesley R.M. Condiff fulfills the dissertation requirement for the doctoral degree in Electrical Engineering approved by Mohammad Arozullah, Ph.D., as Director, and by Sameh Eisharkawy, Ph.D., and Mark Mirotznik, Ph.D. as Readers.

Mohammad Arozullah, Ph.D., Director

Sameh Eisharkawy, Ph.D., Reader

Mark Mirotznik, Ph.D., Reader

# **Table of Contents**

| Architecture and Protocol for Optical Packet Switching                                | ii   |

|---------------------------------------------------------------------------------------|------|

| List of Illustrations                                                                 | v    |

| List of Abbreviations                                                                 | ix   |

| Chapter 1 Introduction                                                                | 1    |

| 1.1 All Optical Networks                                                              | 1    |

| 1.2 Typical Optical Network                                                           | 6    |

| 1.3 Modes of Operation- Advantages of Optical Packet Switching                        | 7    |

| 1.4 Roadblocks to Optical Packet Switching                                            | 8    |

| 1.5 Recent Developments in Optical Memory Size and Processor Speed and their Impa     | act  |

| on Optical Packet Switching                                                           | 8    |

| 1.6 Purpose of Dissertation                                                           | 9    |

| Chapter 2 Optical Packet Switching                                                    | . 10 |

| 2.1 Background                                                                        | . 10 |

| 2.1.1 High Level Architecture of an Optical Packet Switch                             | . 10 |

| 2.1.2 High Level Operation of an Optical Switch                                       | . 12 |

| 2.1.3 Background                                                                      | . 16 |

| 2.1.3.1 Previous Work on Packet Switching                                             | . 16 |

| Chapter 3 Optical Packet Switch Developed in this Dissertation                        | . 32 |

| 3.1 High Level Architecture of a Packet Switch                                        | . 32 |

| 3.2 Current Developments in Enabling Technology for Use in Theses                     | . 33 |

| 3.2.1 Larger Optical Memory                                                           |      |

| 3.2.2 Faster Processing Speed                                                         |      |

| 3.2.3 Numerous Wavelength Division Multiplexing Channels                              | . 37 |

| 3.2.4 Network Processors                                                              | . 37 |

| 3.2.4 Link and Channel Availability Table                                             | . 38 |

| 3.3 Detailed Operational Architecture of Input Side of an Optical Packet Switch       | . 40 |

| 3.5 Flow Diagram of Algorithm of Optical Packet Switch Operation at the Switch Input  | : 43 |

| 3.6 Optical Packet Switch Operation at the Switch Output                              | . 45 |

| 3.7 Flow Diagram of Algorithm of Optical Packet Switch Operation at the Switch Output | ut   |

|                                                                                       | . 46 |

| 3.8.1 Introduction                                                                    | . 47 |

| 3.8.2 Packet Loss Rate                                                                |      |

| 3.8.3 Average Throughput per Line                                                     | . 47 |

| 3.8.4 Total Throughput                                                                |      |

| 3.8.5 Network Throughput                                                              | . 48 |

| Chapter 4 Simulation Models of the Optical Packet Switch                              | . 49 |

| 4.1 List of Architectures Modeled, Simulated and Evaluated                            | . 49 |

| 4.2 Optical Packet Switch Architectures                                               | . 50 |

| 4.2.1 Introduction                                                                    |      |

| Chapter 5 Traffic Flows and Switch Architectures                                      | . 60 |

| 5.1 Baseline Architecture                                                         | 60  |

|-----------------------------------------------------------------------------------|-----|

| 5.2 Single Input Processor Architecture                                           | 62  |

| 5.3 Single Input Processor Architecture with Next Best Route                      | 65  |

| 5.4 Single Input Processor Architecture with Four Wavelength Conversion           |     |

| 5.5 Single Input Processor Architecture with Three Wavelength Conversion          |     |

| 5.6 Single Input Processor Architecture with Two Wavelength Conversion            | 74  |

| 5.7 Single Input Processor Architecture with One Wavelength Conversion            |     |

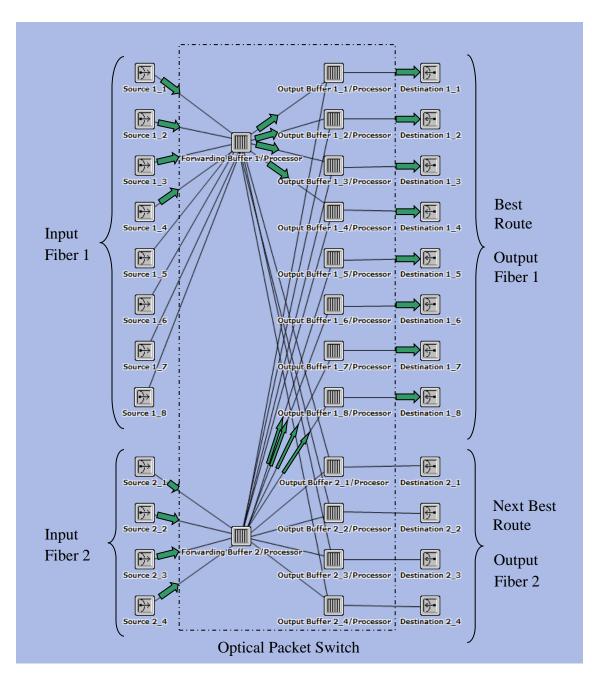

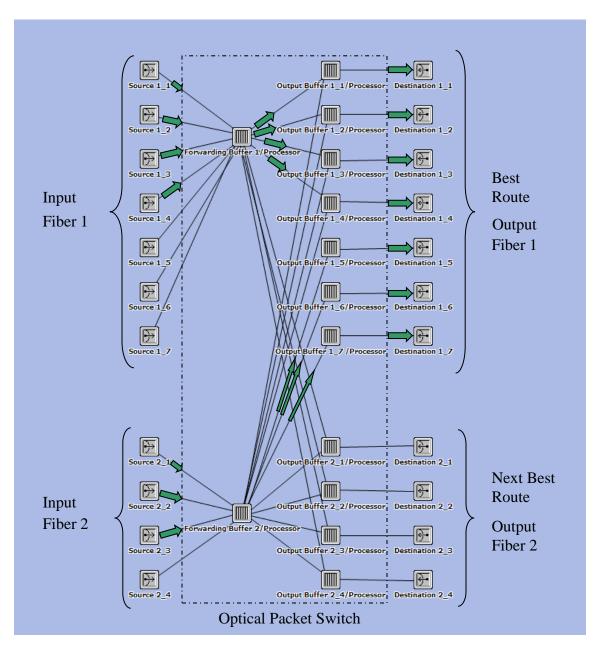

| 5.8 Parallel Input Processors Architecture                                        | 80  |

| 5.9 Parallel Input Processors Architecture with One Wavelength Conversion         | 81  |

| 5.10 Parallel Input Processors Architecture with Two Wavelength Conversion        |     |

| 5.11 Parallel Input Processors Architecture with Three Wavelength Conversion      |     |

| 5.12 Parallel Input Processors Architecture with Next Best Route                  |     |

| 5.13 Parallel Input Processors Architecture with Four Wavelength Conversion       |     |

| 5.14 Description of OPNET Simulation                                              |     |

| Chapter 6 Results                                                                 |     |

| 6.1 Metrics                                                                       |     |

| 6.2 List of Architectures                                                         |     |

| 6.3 List of Group of Architectures                                                |     |

| 6.4 Packet Loss Rate for Single and Parallel Input Processors Architectures       |     |

| 6.5 Average Throughput Per Line for Single and Parallel Input Processors Architec |     |

|                                                                                   |     |

| 6.6 Total Throughput for Single and Parallel Input Processors Architectures       | 104 |

| 6.7 Packet Loss Rates for Single Input Processor Architecture with Wavelength     | 100 |

| Conversion                                                                        | 106 |

| 6.8 Average Throughput per Line for Single Input Processor Architecture with      | 100 |

|                                                                                   | 109 |

| 6.9 Total Throughput for Single Input Processor Architecture with Wavelength      | 110 |

| Conversion                                                                        |     |

| without Next Best Route                                                           |     |

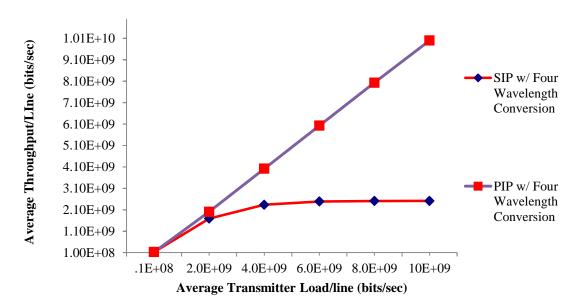

| 6.11 Average Throughput per Line for Single and Parallel Input Processors Archite |     |

| with and without Next Best Route                                                  |     |

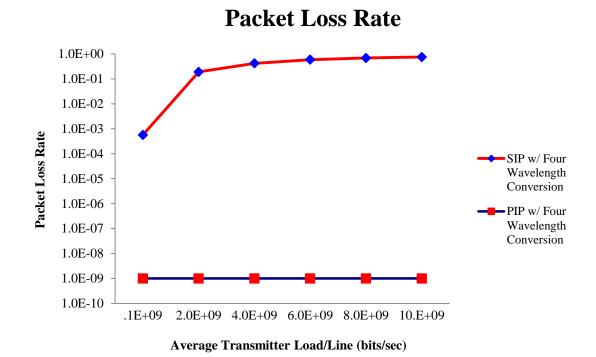

| 6.13 Packet Loss Rate for Parallel Processors Architectures with Wavelength Conv  |     |

| 0.13 Tacket Loss Rate for Faraner Frocessors Architectures with wavelength Conv   |     |

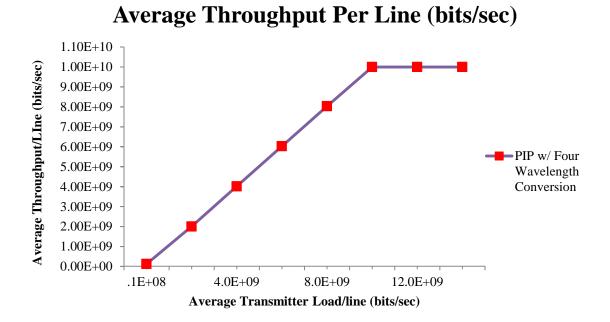

| 6.14 Average Throughput per Line for Parallel Input Processors Architecture with  | 122 |

| Wavelength Conversion                                                             | 125 |

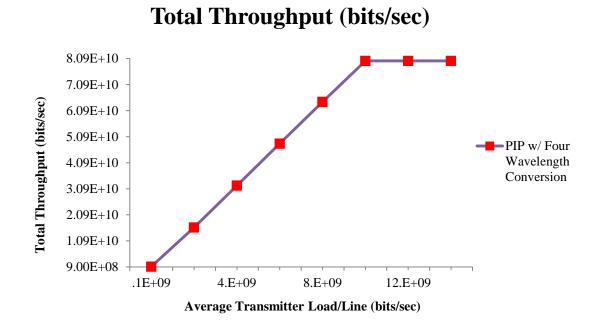

| 6.15 Total Throughput for Parallel Input Processors with Wavelength Conversion.   |     |

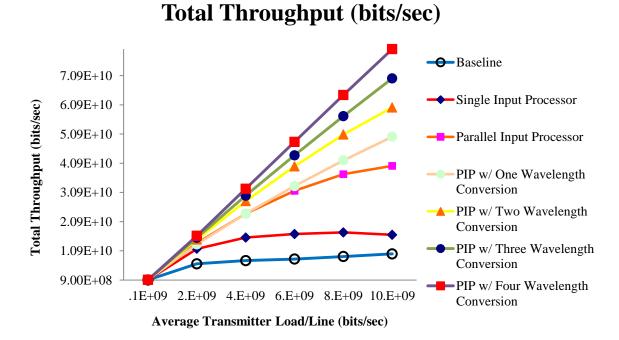

| 6.16 Packet Loss Rate for Parallel Input Processor Architecture with Four Way     |     |

| Conversion                                                                        | 0   |

| 6.17 Average Throughput per Line for Parallel Input Processor Architecture with F |     |

| Wavelength Conversion.                                                            |     |

| 6.18 Total Throughput for Parallel Input Processor Architecture with Four Waveler |     |

| Conversion                                                                        | 0   |

|                                                                                   |     |

| 6.19 Packet Loss Rate for Single and Parallel Input Processors Architectures w   | ith Four     |

|----------------------------------------------------------------------------------|--------------|

| Wavelength Conversion                                                            |              |

| 6.20 Average Throughput for Single and Parallel Input Processors Architectur     | es with      |

| Four Wavelength Conversion                                                       |              |

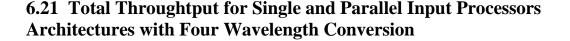

| 6.21 Total Throughtput for Single and Parallel Input Processors Architectures    | with Four    |

| Wavelength Conversion                                                            |              |

| 6.22 Queuing Delay Results                                                       |              |

| 6.23 Packet Loss Rate for Unified Architecture and Parallel Input Processor An   | rchitecture  |

| with Four Wavelength Conversion                                                  |              |

| 6.24 Network Throughput for Unified Architecture with Four Wavelength Con        | nversion and |

| Average Throughput for Parallel Input Processors Architecture with Four Wav      | elength      |

| Conversion                                                                       |              |

| Chapter 7 Results for Single Packet Output Buffer Size vs. Two Packet Output     | Buffer Size  |

|                                                                                  |              |

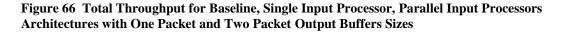

| 7.1 Packet Loss Rate for Single and Parallel Input Processors Architectures with | th One       |

| Packet and Two Packet Output Buffers Sizes                                       |              |

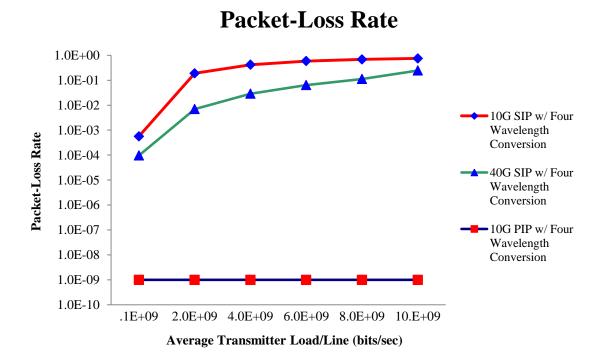

| 7.2 Average Throughput per Line for Single and Parallel Input Processors Arch    |              |

| with One Packet and Two Packet Output Buffer Sizes                               |              |

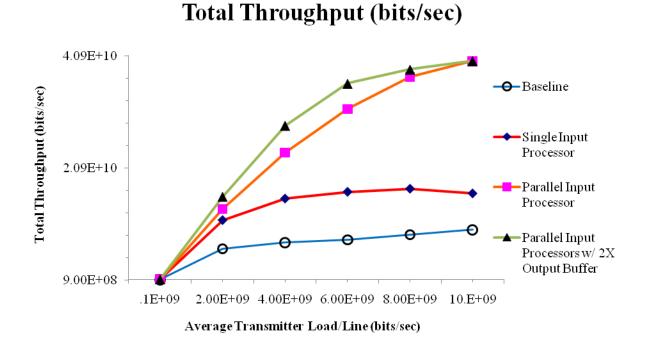

| 7.3 Total Throughput for Single and Parallel Input Processors Architectures wi   |              |

| Packet and Two Packet Output Buffer Sizes                                        | 153          |

| Chapter 8 Hypotheses                                                             |              |

| 8.1 Packet Drop for Single Input Processor Architecture                          | 155          |

| 8.2 Statement of Hypotheses                                                      |              |

| 8.3 Hypotheses Results                                                           |              |

| 8.3.1 Packet Loss Rate for High Power Single Input Processor vs. Low Power       | er Multiple  |

| Input Processors                                                                 |              |

| 8.3.2 Average Throughput per Line for High Power Single Input Processor v        | vs. Low      |

| Power Multiple Input Processors                                                  |              |

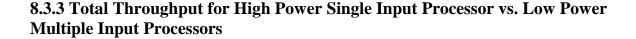

| 8.3.3 Total Throughput for High Power Single Input Processor vs. Low Pow         | ver Multiple |

| Input Processors                                                                 |              |

| Chapter 9 Recommended Architectures                                              |              |

| Chapter 10 Contributions                                                         |              |

| Chapter 11 Conclusions                                                           |              |

| Bibliography                                                                     |              |

|                                                                                  |              |

# List of Illustrations

| Figure 1 A Wavelength Division Multiplexing Link                                      | 3  |

|---------------------------------------------------------------------------------------|----|

| Figure 2 A Typical All Optical Network                                                | 6  |

| Figure 3 High Level Architecture of the Optical Packet Switch                         | 10 |

| Figure 4 Detailed Operational Architecture of Input Side of an Optical Packet Switch  | 12 |

| Figure 5 Detailed Operational Architecture of Output Side of an Optical Packet Switch | 14 |

| Figure 6 Unified Study's Node Architecture in an Unslotted Network [25]               | 17 |

| Figure 7 Unified Study's Topology 1 and Topology 2 [25]                               | 19 |

| Figure 8 The Unified Probability Distribution Function of IP Packet Sizes [25]            | 20       |

|-------------------------------------------------------------------------------------------|----------|

| Figure 9 Wavelength Conversion Results for the Unified Study [25]                         | 22       |

| Figure 10 Unified Study's Results for Optical Buffering and Deflection [25]               | 24       |

| Figure 11 Unified Study Results for Combinational Architectures [25]                      | 26       |

| Figure 12 Functional Diagram for All-Optical Contention Resolution Method [26]            | 28       |

| Figure 13 Experimental Setup for 160 Gb/s All-Optical Contention Resolution [26]          | 29       |

| Figure 14 BER Performance for 160 Gbps Contention Resolution Scheme [26]                  | 31       |

| Figure 15 High Level Architecture for Optical Packet Switch [1]                           | 32       |

| Figure 16 Detailed Operational Architecture of Input Side of an Optical Packet Switch     | 40       |

| Figure 17 Flow Diagram of Algorithm of Optical Packet Switch Operation at the Switch      |          |

| Input                                                                                     |          |

| Figure 18 Flow Diagram of Algorithm of Optical Packet Switch                              | 46       |

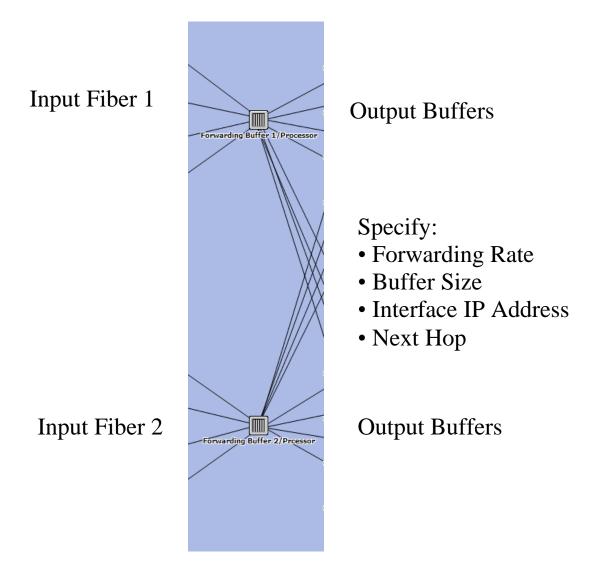

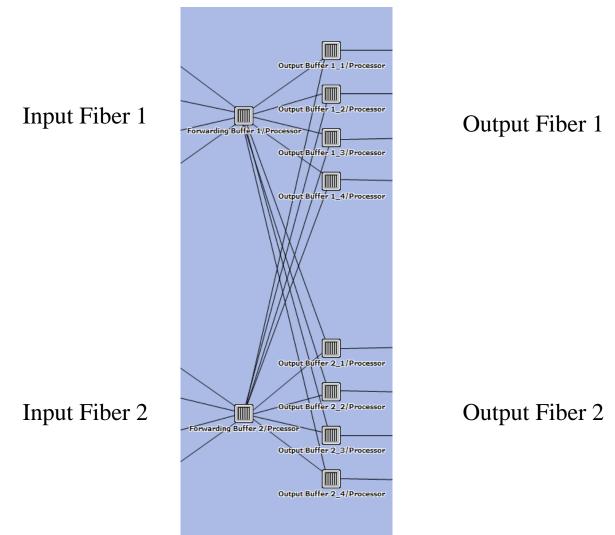

| Figure 19 Graphical Representation of Forwarding Buffers in OPNET Modeler                 | 51       |

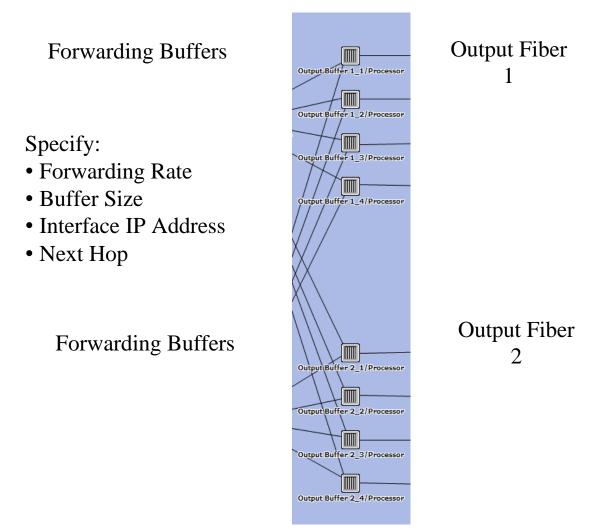

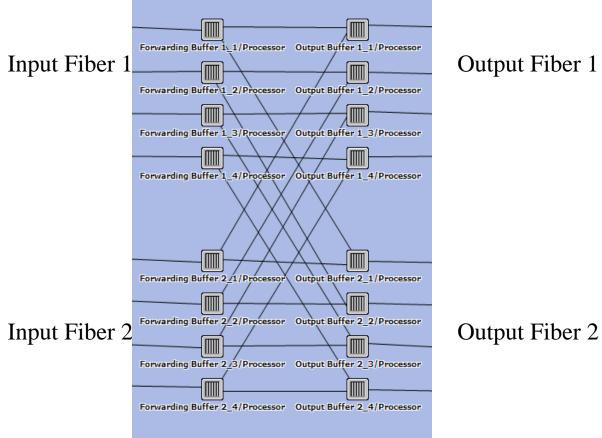

| Figure 20 Graphical Representation of Output Buffers in OPNET Modeler                     | 53       |

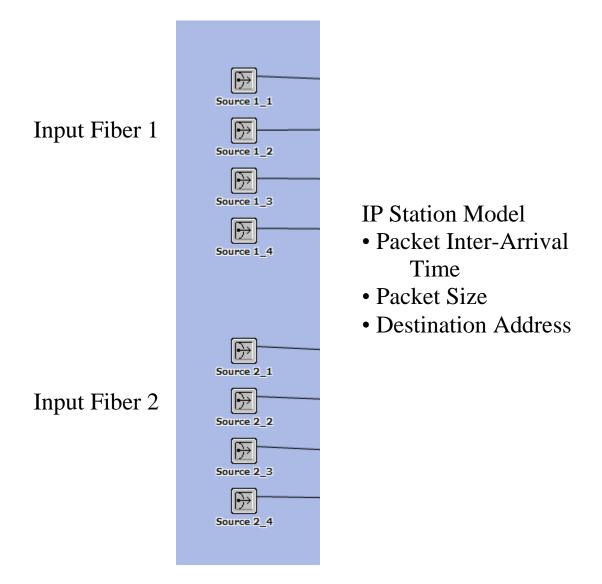

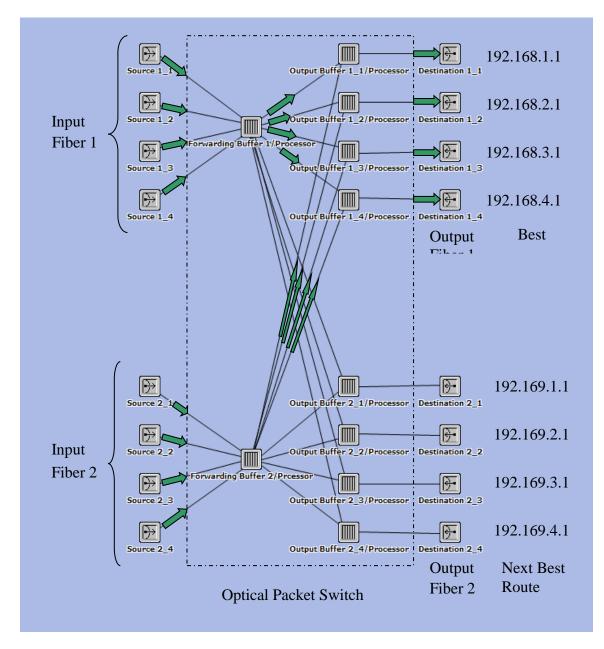

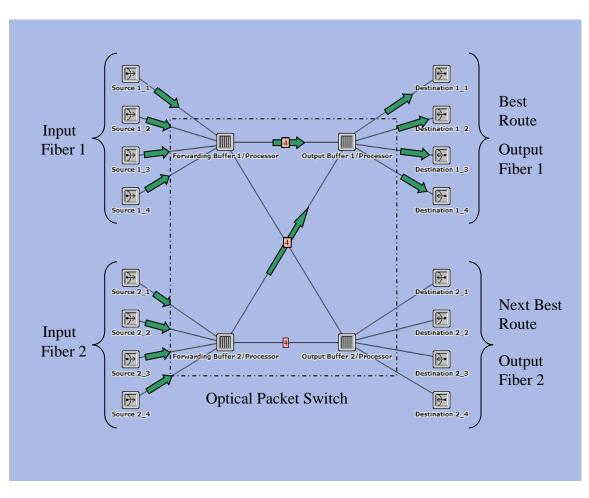

| Figure 21 Graphical Representation of Source Models in OPNET Modeler                      | 54       |

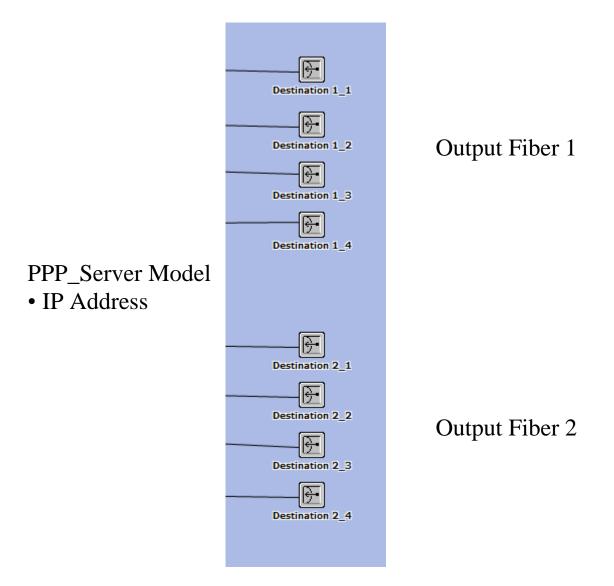

| Figure 22 Graphical Representation of Destination Models in OPNET Modeler                 | 55       |

| Figure 23 Single Input Processor Configuration                                            |          |

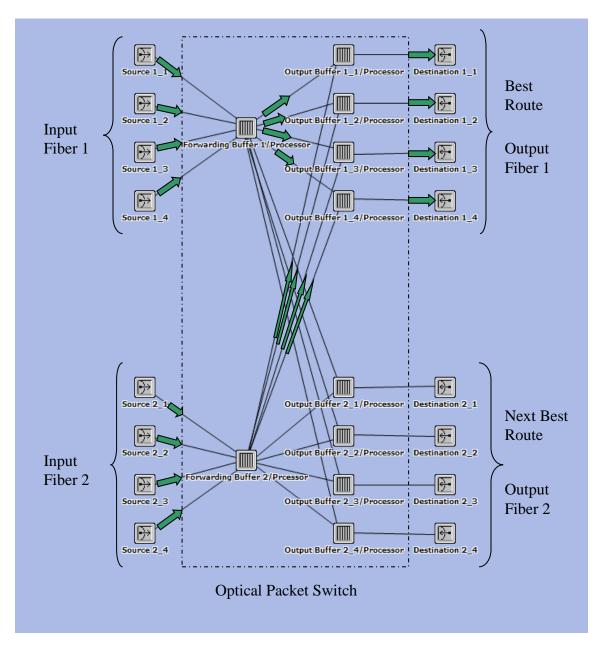

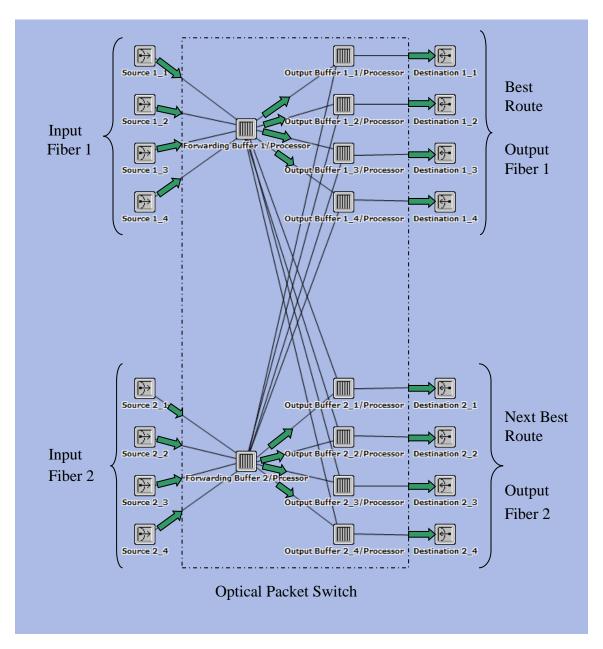

| Figure 24 Parallel Input Processor Configuration                                          | 57       |

| Figure 25 Routing Operation within Optical Packet Switch Model                            | 58       |

| Figure 26 Switch Architecture and Traffic Flow for Baseline Architecture                  | 61       |

| Figure 27 Switch Architecture and Traffic Flow for Single Input Processor Architecture    | 63       |

| Figure 28 Switch Architecture and Traffic Flow for Single Input Processor Architecture w  | vith     |

| Next Best Route                                                                           | 66       |

| Figure 29 Switch Architecture and Traffic Flow for Single Input Processor with Four       |          |

| Wavelength Conversion                                                                     | 69       |

| Figure 30 Switch Architecture for Single Input Processor Architecture with Three          |          |

| Wavelength Conversion and the Traffic Flow for Fiber 1 and the First, Second, and Third   | l        |

| Source of Fiber 2                                                                         |          |

| Figure 31 Switch Architecture for Single Input Processor with Three Wavelength Conver-    |          |

| and the Traffic Flow for the Fourth Source of Input Fiber 2                               |          |

| Figure 32 Switch Architecture for Single Input Processor Architecture with Two Waveler    | 0        |

| Conversion and the Traffic Flow for Input Fiber 1 and the First and Second Source of Inp  | ut       |

| Fiber 2                                                                                   | 75       |

| Figure 33 Switch Architecture for Single Input Processor Architecture with Two Waveler    | <u> </u> |

| Conversion and the Traffic Flow for the Third and Fourth Source of Input Fiber 2          |          |

| Figure 34 Switch Architecture and Traffic Flow for Single Input Processor Architecture w  |          |

| One Wavelength Conversion                                                                 |          |

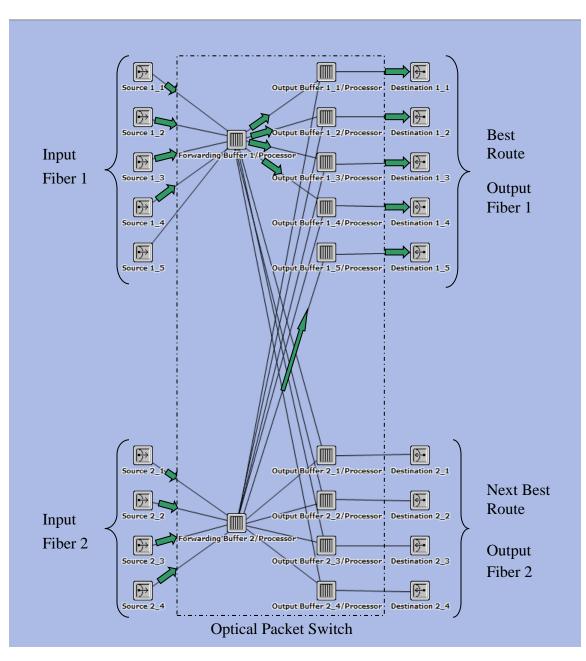

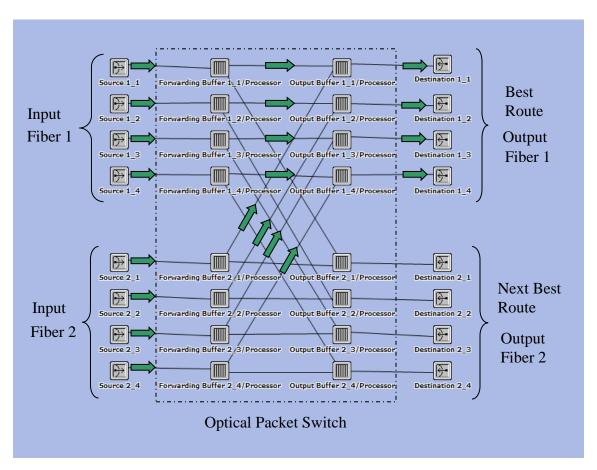

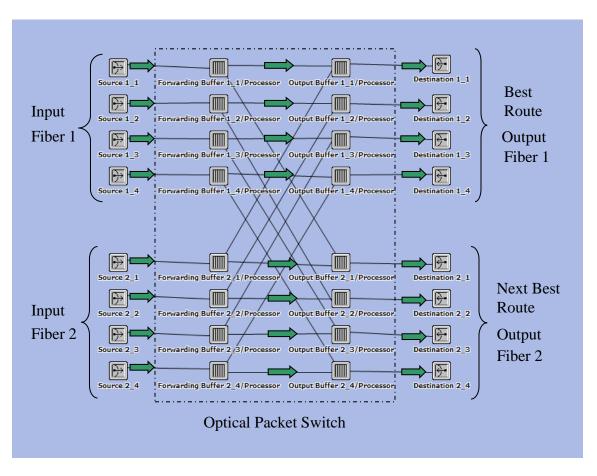

| Figure 35 Switch Architecture and Traffic Flow for Parallel Input Processors Architecture | e 81     |

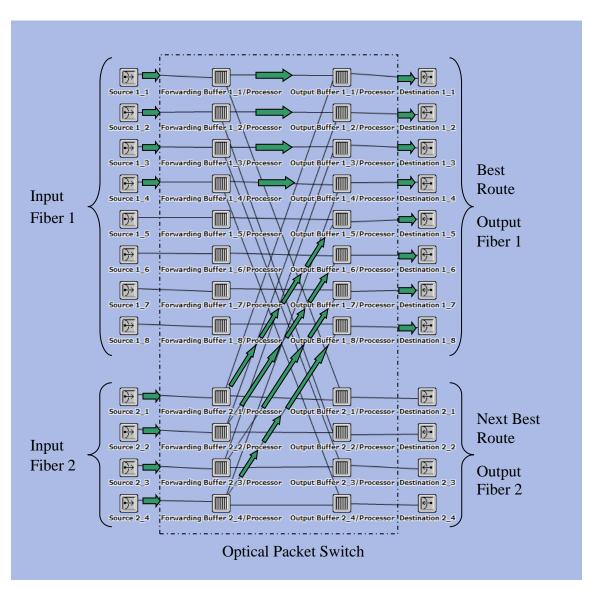

| Figure 36 Switch Architecture and Traffic Flow for Parallel Input Processors One          |          |

| Wavelength Conversion                                                                     | 83       |

| Figure 37 Switch Architecture for Parallel Input Processors Architecture with Two         | _        |

| Wavelength Conversion and the Traffic Flow for Fiber 1 and the First and Second Source    |          |

| Fiber 2                                                                                   | 85       |

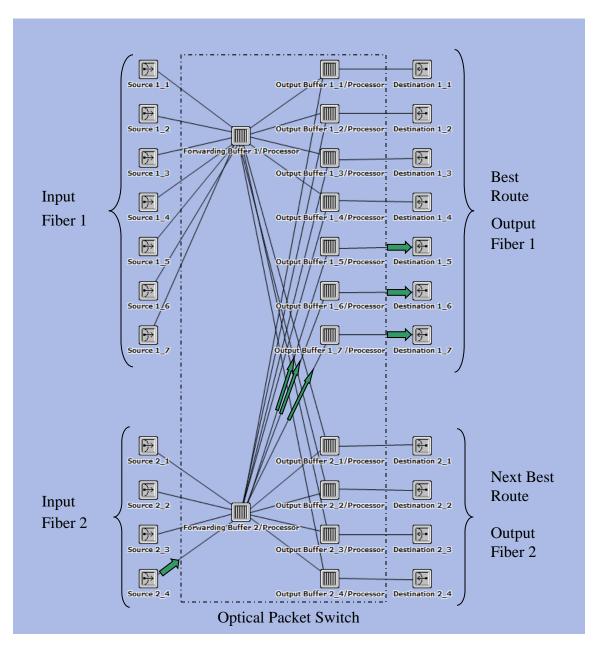

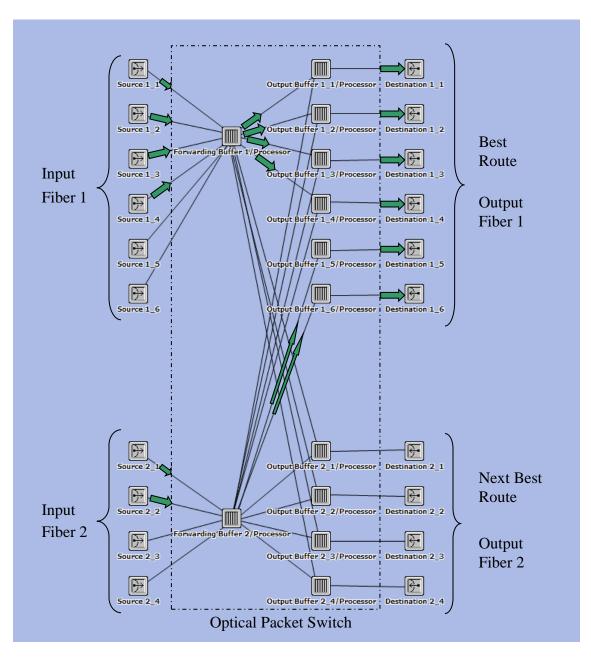

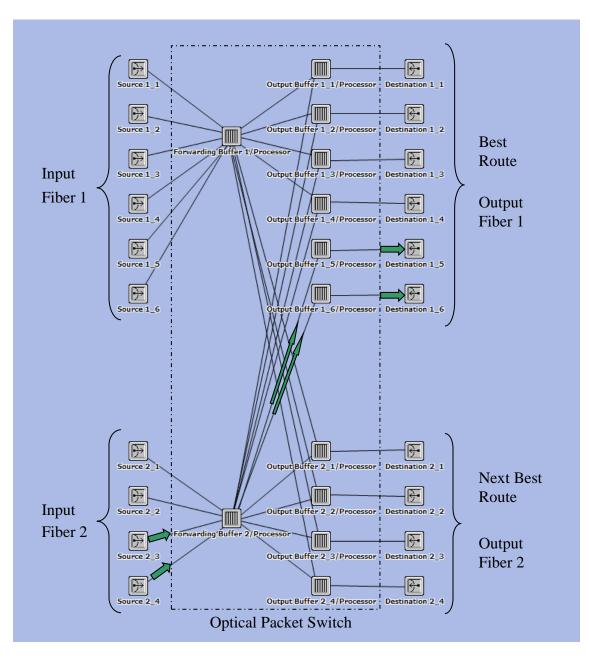

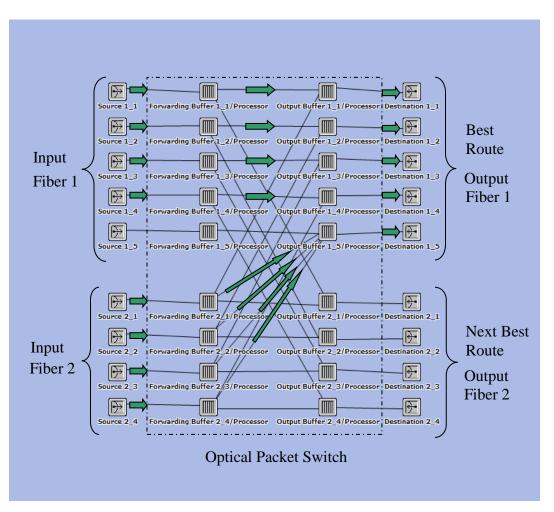

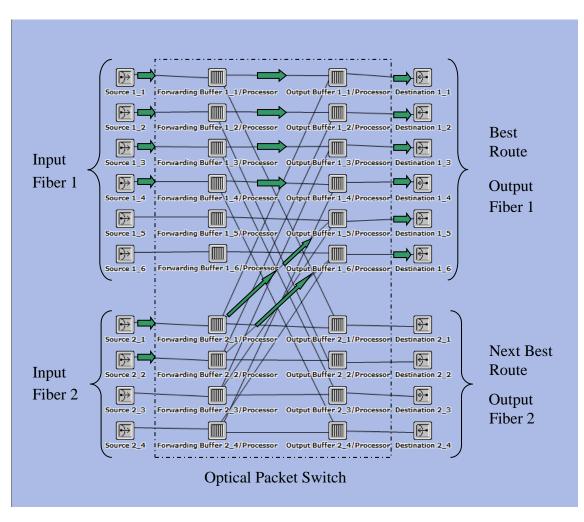

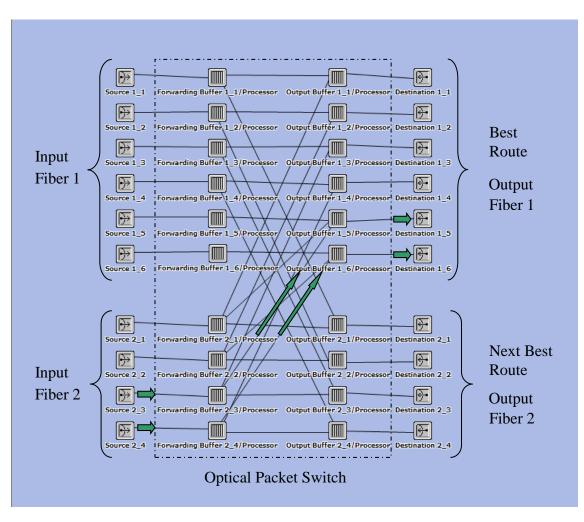

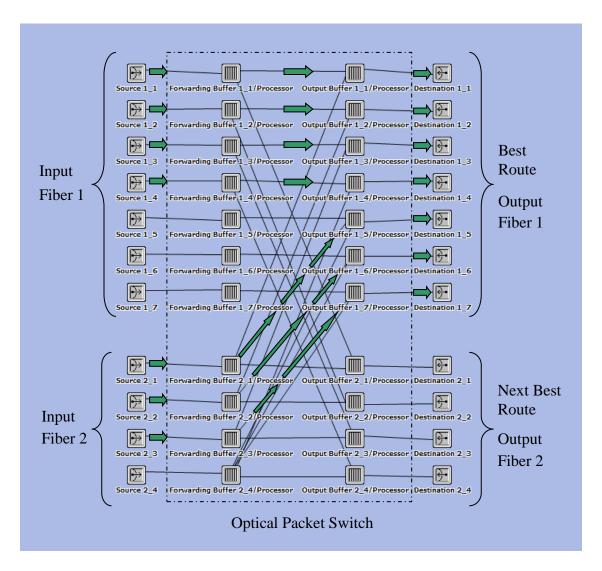

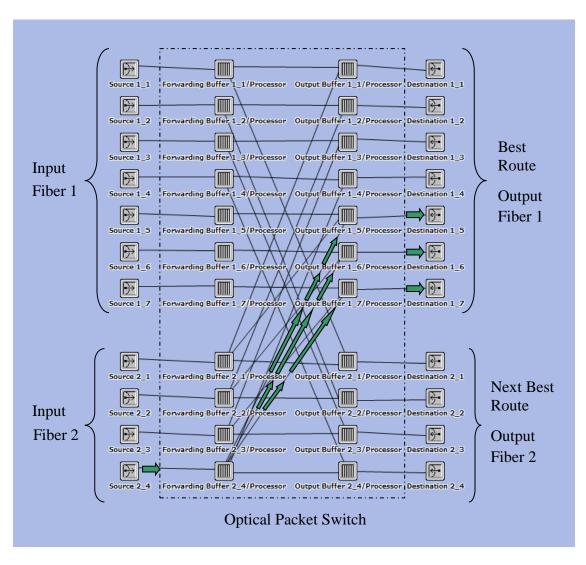

| Figure 38 Switch Architecture for Parallel Input Processors Architecture with Two<br>Wavelength Conversion and the Traffic Flow for the Third and Fourth Source of Fiber 2 86<br>Figure 39 Switch Architecture for Parallel Input Processors Architecture with Three<br>Wavelength Conversion and the Traffic Flow for Fiber 1 and the First, Second and Third<br>Source of Fiber 2 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 40 Switch Architecture for Parallel Input Processors Architecture with Three<br>Wavelength Conversion and the Traffic Flow for the Fourth Source of Fiber 2                                                                                                                                                                                                                  |

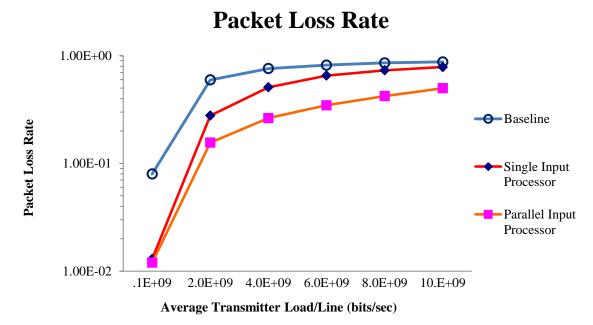

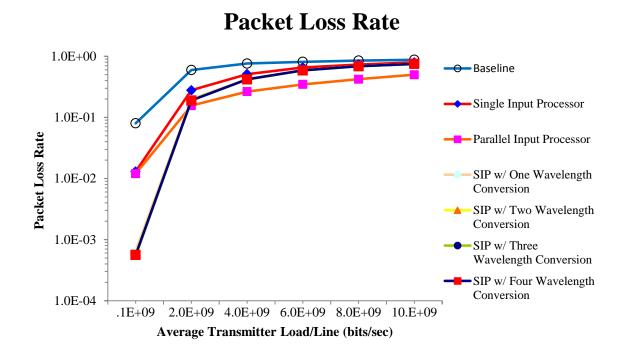

| Figure 43 Packet Loss Rate for Baseline, Single and Parallel Input Processors Architectures                                                                                                                                                                                                                                                                                         |

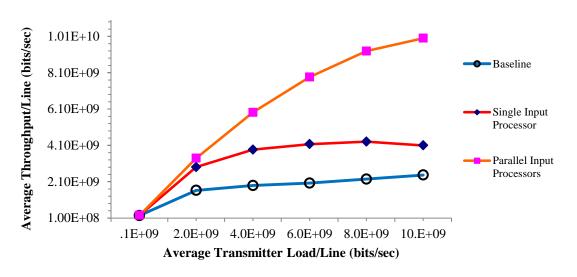

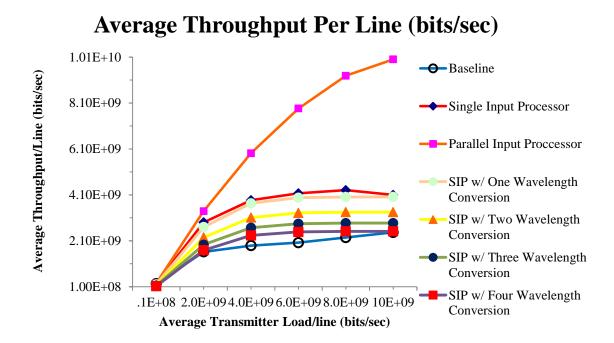

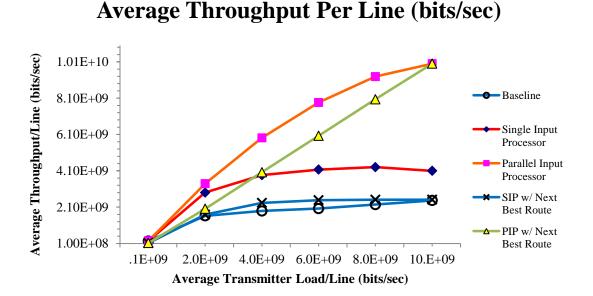

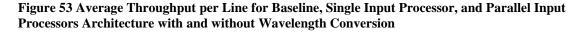

| Figure 44 Average Throughput per Line for Baseline, Single and Parallel Input Processors<br>Architectures                                                                                                                                                                                                                                                                           |

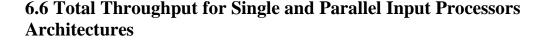

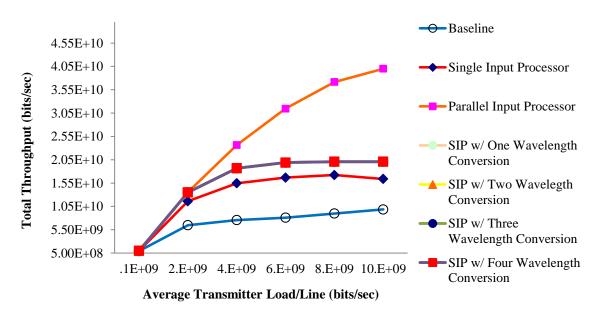

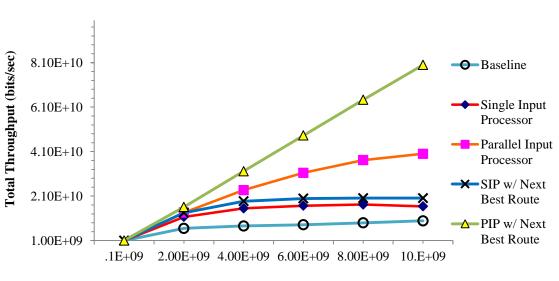

| Figure 45 Total Throughput for Baseline, Single and Parallel Input Processors Architectures 104                                                                                                                                                                                                                                                                                     |

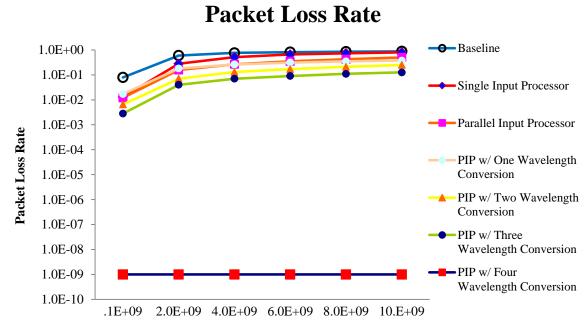

| Figure 46 Packet Loss Rates for Baseline, Single Input Processor Architecture with and without Wavelength Conversion, Parallel Input Processors Architecture                                                                                                                                                                                                                        |

| with and without Wavelength Conversion, and Parallel Input Processors Architecture 109<br>Figure 48 Total Throughput for Baseline, Single Input Processor Architecture with and                                                                                                                                                                                                     |

| without Wavelength Conversion, and Parallel Input Processors Architecture                                                                                                                                                                                                                                                                                                           |

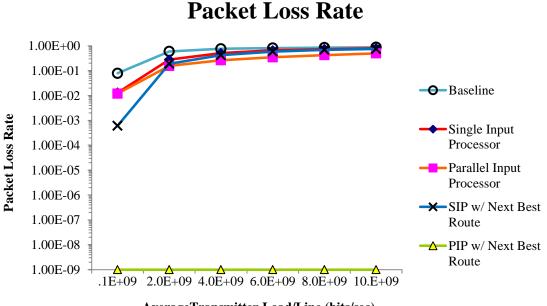

| Architectures with and without Next Best Route                                                                                                                                                                                                                                                                                                                                      |

| with and without Next Best Route                                                                                                                                                                                                                                                                                                                                                    |

| Architectures with and without Wavelength Conversion                                                                                                                                                                                                                                                                                                                                |

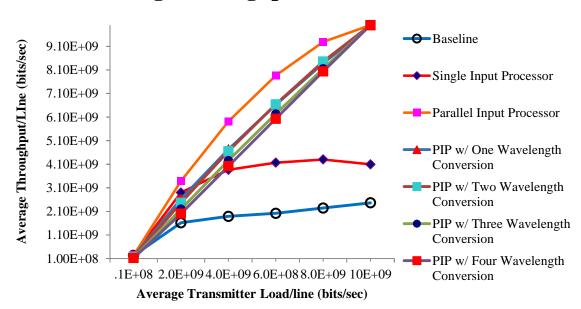

| Input Processors Architecture with and without Wavelength Conversion                                                                                                                                                                                                                                                                                                                |

| Processors with and without Wavelength Conversion                                                                                                                                                                                                                                                                                                                                   |

| Conversion                                                                                                                                                                                                                                                                                                                                                                          |

| Wavelength Conversion                                                                                                                                                                                                                                                                                                                                                               |

| Conversion                                                                                                                                                                                                                                                                                                                                                                          |

| Wavelength Conversion                                                                                                                                                                                                                                                                                                                                                               |

| Figure 59 Average Throughput for Single and Parallel Input Processors Architectures with    |

|---------------------------------------------------------------------------------------------|

| Wavelength Conversion                                                                       |

| Figure 60 Total Throughput for Single and Parallel Input Processors Architectures with Four |

| Wavelength Conversion                                                                       |

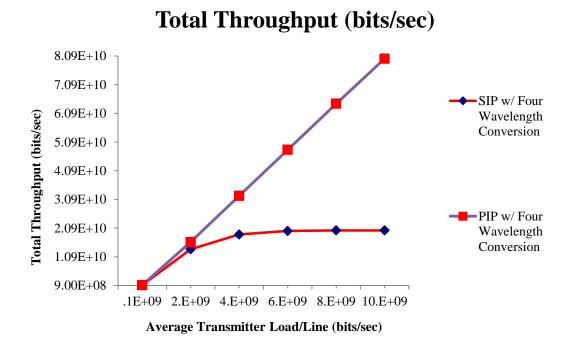

| Figure 61 Queuing Time Delay for Processor for Conflict                                     |

| Figure 62 Packet Loss Rates for Unified Architecture and Parallel Input Processor           |

| Architecture with Four Wavelength Conversion                                                |

| Figure 63 Network Throughput for Unified Architecture with Four Wavelength Conversion       |

| Average Throughput Per Line for Parallel Processors Architecture with Four Wavelength       |

| Conversion                                                                                  |

| Figure 64 Packet Loss Rate for Single and Parallel Input Processors Architectures with One  |

| Packet and Two Packet Output Buffer Sizes                                                   |

| Figure 65 Average Throughput per Line for Single and Parallel Input Processors              |

| Architectures with One Packet and Packet Output Buffer Sizes                                |

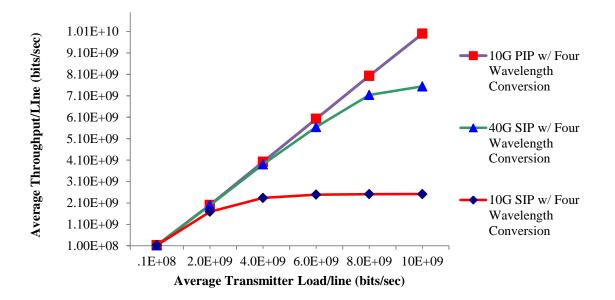

| Figure 66 Total Throughput for Baseline, Single Input Processor, Parallel Input Processors  |

| Architectures with One Packet and Two Packet Output Buffers Sizes                           |

| Figure 67 Packet Loss Rate for High Power Single Input Processor vs. Low Power Multiple     |

| Input Processors                                                                            |

| Figure 68 Average Throughput per Line for High Power Single Input Processor vs. Low         |

| Power Multiple Input Processors                                                             |

| Figure 69 Total Throughput for High Power Single Input Processor vs. Low Power Multiple     |

| Input Processors                                                                            |

# **List of Abbreviations**

2X - two timesASIC – Application-specific Integrated Circuit BCAM – Binary content addressable memory BER – Bit Error Rate CA – Channel Availability CAM - Content addressable memory Db - decibels DWDM – Dense Wavelength Division Mutlitplexing FIFO – First in, first out FS – Forwarding Speed Gbps - Gigabits per second GHz - Gigahertz GMPLS - Generalized Multi Protocol Lambda Switching IP – Internet Protocol IPv6 – Internet Protocol version 6 ITU - International Telecommunication Union LUT – Look up table Mlps – Mega Look-ups per second mm - millimeters MPLS - Multi Protocol Lambda Switching NBR - Next Best Route Ns – nano seconds O/E/O – optical-electrical-optical conversion OL - Output Line Buffer OSPF - Open Shortest Path First PBRS – Pseudorandom binary sequence PPP – Point-to-Point **PS** - Picoseconds RAM - Random access memory TCAM – Ternary addressable memory V - Volts

W – watts

## **Chapter 1 Introduction**

This dissertation proposes a number of single and parallel processor architectures and protocols for optical packet switching in all optical networks making use of a number of recent advances in high speed processors and optical buffers and a number of packet contention resolution techniques in wavelength, time, and space, alternative routing and processing speeds.

#### **1.1 All Optical Networks**

In all optical networks, electrical information is converted into optical form at the source. The information remains in optical form during its transmission to the destination. There is no optical to electrical to optical (O/E/O) conversion at the intermediate nodes. All switching, amplification and buffering are to be done in the optical domain. There are two ways of information transmission, namely using end to end optical light path establishment and optical packet switching. In the past optical packet switching has been difficult to implement due the lack of availability of optical buffers of required size. Thus emphasis has been given to light path establishment before transmitting information. However, optical packet switching provides a number of advantages over the light path establishment method. Firstly, in a large network a light path may consist of interconnection of a number of optical links. Thus establishment, maintenance and simultaneous obligation of all required resources over long light paths may be problematic. This is not required for packet switching. In packet switching packets are transmitted and switched dynamically at each node using the resources available at that node. At any time only the resources needed for connecting to the next node are obligated. Secondly, In case of congestion a new light path may be needed to be established. Thus in a heavily loaded network frequent establishment and reestablishment of such light paths are needed. On the other hand in packet switching packets can be dynamically routed around congestion by updating routing tables at the nodes. This may lead to lower delay for packets. Thirdly, packet switching uses fewer resources as at any time only the resources between a transmitting node and the next node are in use, whereas in light path method all the resources between all the nodes in a light path are in use as long as the light path is maintained. Fourthly, in light path establishment method sometimes resources may be not be utilized as the whole path need to be maintained irrespective of whether data is transmitted over it or not, whereas in packet switching resources are obligated only when they are used.

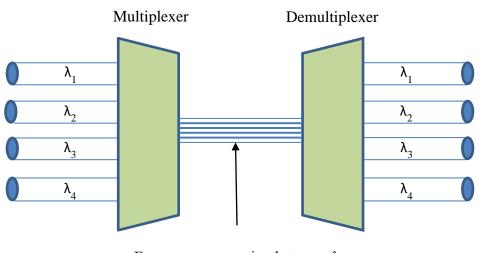

Many current deployed optical networks use wavelength division multiplexing (WDM). WDM is based on frequency division multiplexing. In frequency division multiplexing, the bandwidth of a channel is divided into multiple channels. Each channel occupies part of the larger frequency spectrum. WDM has similar concepts. A channel is called a wavelength. This terminology comes from each channel at a different wavelength. Wavelengths on optical fiber are separated by unused optical spectrum. Figure 1 illustrates a simple example of a WDM link. Four optical fibers are connected to a WDM multiplexer. The WDM multiplexer combines or multiplexes the four optical fibers into one optical fiber. The inverse operation occurs at the receiving multiplexer. The receiving multiplexer is commonly called a demultiplexer. The demultiplexer separates the wavelengths and sends the wavelengths to an appropriate output port. The output port may be another optical fiber.

Frequency separation between  $\lambda s$  can be 100, 50, or 25 GHz

#### Figure 1 A Wavelength Division Multiplexing Link

As Figure 1 illustrates, each wavelength is separated by unused optical spectrum. This prevents the signals from interfering with each other signal. The International

Telecommunication Union (ITU) has published standards on the spacing. The most common spacing is 100 GHz spacing. This was specified in the first ITU-T specification for WDM in Recommendation G.692, Optical Interfaces for Multichannel Systems with Optical Amplifiers. Recommendation G.692 has alternative spacing of 50 GHz and 200 GHz. Recommendation G.692 applies to 4, 8, and 16 channel WDM systems [1]-[4].

Dense Wave Division Multiplexing (DWDM) has the multiplexing of more than 160 channels with data rates of 10 gigabits per second (Gbps). The channel spacing for DWDM is 25 GHz. The total data rate for 160 channel DWDM system is 1.6 terabits per second (Tbps). DWDM systems with 320 channels and a total data rate of 3.2 terabits have been proposed [1]-[3].

Currently, in order to perform switching in WDM systems, optical packets must be converted to electrical packets. The electrical packet is then forwarded to the appropriate output port. The electrical packet is then converted back to an optical packet. Electrical switches and routers cannot forward packets at the data rates required by DWDM systems. This is commonly known as the optical electrical optical (O/E/O) bottleneck..

In all optical networks, electrical information is converted into optical information at the source. The information remains optical information during the transmission to the

destination. There is no optical to electrical to optical (O/E/O) conversion at the intermediate nodes. All switching, amplification and buffering needs to be done in the optical domain.

An all-optical network will provide fast automatic setup and teardown of paths across the optical network. This requires an implementation of a dynamically reconfigurable optical transport layer based on fast optical cross connects (OXCs) that are coupled with a suitable control and management architecture. The optical transport network (OTN) will be capable of supporting large numbers of high-capacity channels with data rates on the order of 10 - 40 gigabits per second (Gbps) [5].

Additional information on all-optical packet switched networks can be found in [6]-[12].

### **1.2 Typical Optical Network**

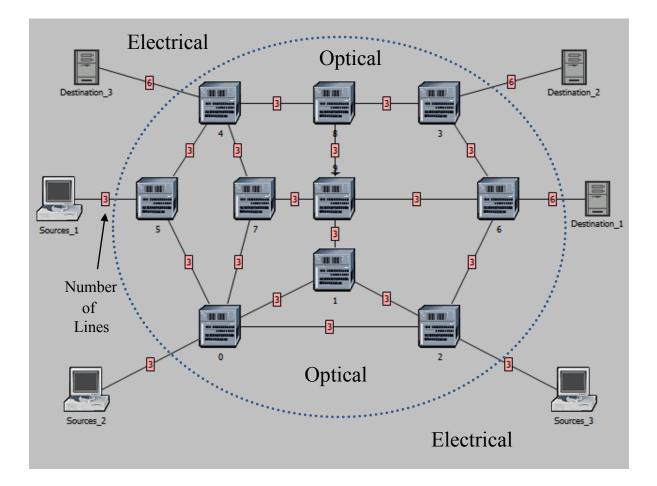

#### Figure 2 A Typical All Optical Network

The typical optical network is shown above in Figure 2. The typical optical network has a number of sources and destinations that are connected to it. The all optical network contains a number of optical switches, multiplexers, and demultiplexers. Add the functions of the switches. The sources and destinations process packets electrically. Packets are generated electrically at the source. The packets undergo an electrical to optical conversion after packets leave the source. The packets are forwarded and routed optically. The packets are

converted from being an optical packet to an electrical packet at the last hop to the packet's destination.

#### **1.3 Modes of Operation- Advantages of Optical Packet Switching**

The modes of operation are light path switching (circuit switching) and packet switching. Light path switching requires end-to-end light paths to be established, maintained, and terminated. Resources need to be reserved for the entire light path. Light path switching uses Generalized Multiprotocol Label Switching Protocols (GMPLS) and reservation protocols to reserve resources. Difficulties exist in the establishment and maintenance of many required light paths that are simultaneous, and required, especially in large networks. However, once a light path is established, the information can be transmitted quickly. Optical packet switching is a potential transport solution to close the gap between the electrical (IP/MPLS) layer and the optical (DWDM) layer. Messages are broken into small packets. The packets are transmitted over independent paths. There is no need to establish end-to-end paths. There is no need to reserve resources end to end.

This can avoid congestion and failures in the network. Resources are dynamically and locally assigned and released. Thus, packet switching has the ability to dynamically allocate network resources with fine granularity and with excellent scalability.

#### 1.4 Roadblocks to Optical Packet Switching

It is beneficial to use packet switching rather than light path switching. However the packet switching needs to satisfy two requirements. The first requirement is to have transparency to packet size. The optical packet switching network needs be able to handle packets of varying sizes. The second requirement is to handle packet arriving asynchronously at high speed. Optical Packet switching needs optical buffers to store and forward packets. Large optical buffer is hard to come by. This limits input data rate and throughput. There is possible packet loss due to packet conflict and overflow of the buffer. There is a need to have conflict reduction and/or resolution schemes. The trend has been to use light paths with resource reservation in spite of the associated problems.

### **1.5** Recent Developments in Optical Memory Size and Processor Speed and their Impact on Optical Packet Switching

Some Recent developments have increased the feasibility of optical packet switching.

There are better optical buffers. Currently there is a reported available non-recirculating optical buffer with a size of 793 ns [5]. This optical buffer with a longer time delay will allow more time to find a route for an optical packet. There are improved high-speed processors for routing table look up. Currently available table look up rates is 213.4 Mlps for IPv6 packet with 128 bit addresses [6]. This is sufficient to satisfy high speed link OC-768 (40 Gbps) with 150000 routing entries. This faster routing table look up system will allow more routes for the optical packet to be looked up per unit time. There is a 5 GHz memory

read/write system [7]. This development will enable routing tables to be updated at a higher rate. There is high-speed optical switching. Wavelength division multiplexing/demultiplexing now has many channels. Dense wavelength division multiplexing can have up 320 channels.

#### **1.6 Purpose of Dissertation**

The purpose of the dissertation is to develop high speed optical packet switch using packet contention reduction and contention resolution techniques. The packet contention reduction and contention techniques will be taking advantage of available higher speed processors and implementing a number of contention resolution methods in time (larger buffer size), wavelength (conversion), and space (Next Best Route). The contention resolution methods will be using dynamically updated Link & Channel Availability Table and dynamically updated hierarchical Routing Table (OSPF, Next Best Route). There will be many WDM channels available per fiber. Packets will be delayed rather than saving the full packet. Preambles will be added to reduce the delaying needed for data portion of packet.

# **Chapter 2 Optical Packet Switching**

### 2.1 Background

### 2.1.1 High Level Architecture of an Optical Packet Switch

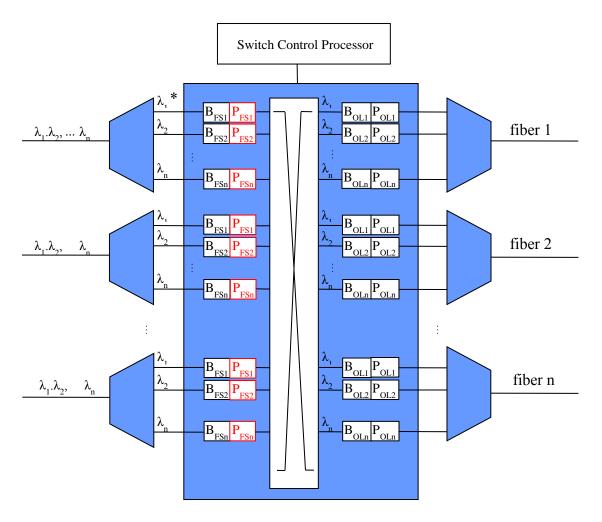

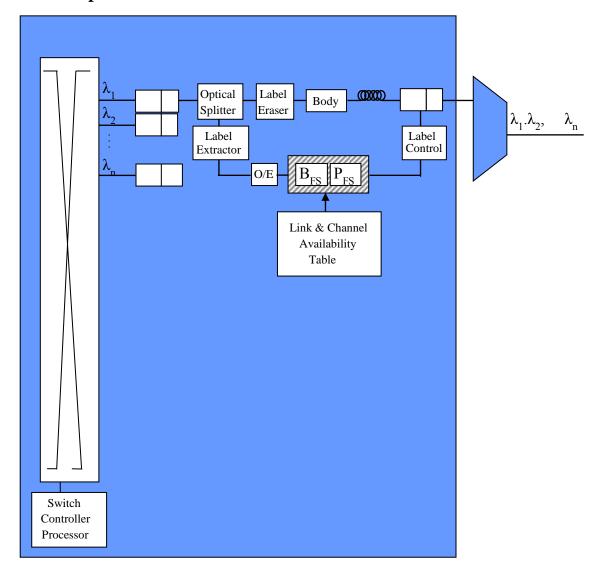

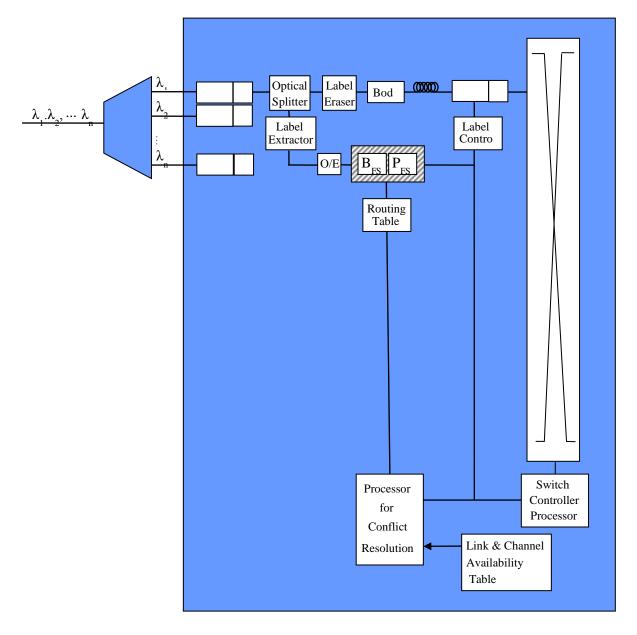

The high level architecture of the optical packet switch is shown above in Figure 3. Packets are arriving at the demultiplexer on each input fiber. The demultiplexer separates the incoming packets into separate channels. Each input and output fiber contains N active

channels and M spare channels. The center frequency on the input side of the switch is denoted by  $\lambda_{kl}^{i}$  on the l-th channel on the k-th fiber. The center frequency on the output side of the switch is denoted by  $\lambda_{kl}^{o}$  on the l-th channel on the k-th fiber. The packet interarrival time is known. Each input channel has one forwarding buffer and one processor. When the packet arrives to the input buffer the packet header is separated and converted to electrical information. A route is found for the packet while the packet body is delayed optically in the buffer. Once a route is found for the packet, the switch is configured by the Switch Control Processor and a new label written just as the packet is leaving the optical buffer. The packet is forwarded to the output buffer. At the output buffer the packet and a new label is written for the packet and attached the packet as the packet leaves the output buffer. The packet is then multiplexed with other channels in the multiplexer at the switch output and forwarded to the next switch.

### 2.1.2 High Level Operation of an Optical Switch

# 2.1.2.1 Input Side

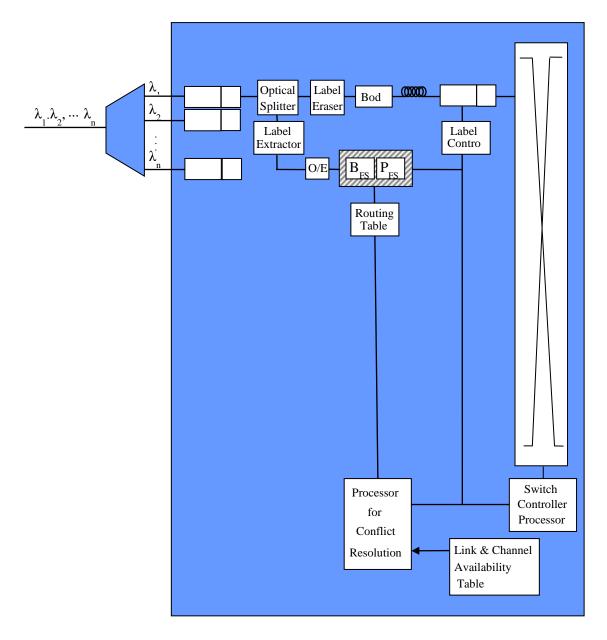

The detailed operational architecture of the input side of an optical packet switch is shown on the previous page in Figure 4. Packets arrive to the switch asynchronously at the switch's demultiplexer. The packets are de-multiplexed and passed through an optical splitter. On one path from the optical splitter the label is erased from the packet and the packet is delayed in the optical buffer. On the other path from the optical splitter, the label is extracted from the packet. The label is then converted from optical information to electrical information in the O/E converter. The packet label is then sent to electrical buffer B<sub>FS</sub>. The buffer's processor reads the packet header. The processor consults the routing table to find route for the packet. If a route cannot be found, the Processor for Conflict is consulted. The Processor for Conflict has route availability information from the Link and Channel Availability Table. Once a path is found, the revised packet label is sent to the label controller and the switch controller. The label controller generates an optical label when the packet exits the optical buffer. The switch controller sets up a path to an output buffer for the packet to be sent.

### 2.1.2.2 Output Side

Figure 5 Detailed Operational Architecture of Output Side of an Optical Packet Switch

The detailed operational architecture of the output side of an optical packet switch is shown above in Figure 5. The optical packet arrives at the output fiber. The optical packet is passed through an optical splitter. On one path from the optical splitter the label is erased from the packet and the packet is delayed in the optical buffer. On the other path from the optical splitter, the label is extracted from the packet. The label is then converted from optical information to electrical information. The packet label is then sent to electrical buffer  $B_{FS}$ . The buffer's processor compares the packet label with available routes. The processor consults the Link and Availability Table to find route for the packet. Once a path is found the revised packet label is sent to the label controller. The label controller generates an optical label when the packet exits the optical buffer. The optical packet is multiplexed with other packets and sent to its next hop.

#### 2.1.3 Background

#### 2.1.3.1 Previous Work on Packet Switching

#### 2.1.3.1.1 Unified Study

The paper entitled, "A Unified Study of Contention-Resolution Schemes in Optical Packet-Switched Networks," presents a comprehensive study of contention-resolution schemes in an optical packet-switched network. The objective of the study is to provide a unified study of a network of optical routers. The study includes contention resolution in wavelength, time, and space dimensions. The study has three main areas. The first main area is how to accommodate all three dimensions of contention resolution in an integrated optical router. The second main area is how the performance of the three dimensions compares with each dimension. The final area is how various combinational schemes can be architected and how the combinational schemes perform. Simulation experiment results capture the characteristics of different contention-resolution schemes. The simulation results quantify the upper-bound average offered transmitter load for the simulated schemes [25].

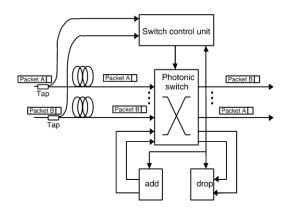

Figure 6 Unified Study's Node Architecture in an Unslotted Network [25]

Figure 6 to the left shows the general node architecture and packet behavior for unslotted networks in the Unified Study. The fixedlength fiber delay lines are used to hold the packet when the header is being processed and the switch fabric is configured to route the packet. All packets have the same amount of time delay with the same relative position in

which they arrived, unless packet contention occurs. Each node has a number of add/drop ports. The number of drop/add ports will depend on the nodal degree. Each drop/add ports will correspond to multiple client interfaces reflecting multiple wavelengths on each fiber. Every input interface on the switches will be connected to a local receiver. Every output interface on the switches will be connected to a transmitter. Different contention-resolution schemes give lead to different architectures. The contention resolution schemes are wavelength conversion, single or multi-wavelength buffering, deflection, reservation of path ahead, no contention resolution, and delay for reservation [25].

Optical buffering utilizes one or more optical fiber delay lines to loop the signal from the output back to the input of the switch fabric. The study considers both single-wavelength and multi-wavelength optical buffering. The single-wavelength optical buffer is when the delay line can only take one packet at a time. The multiple-wavelength buffer is when each

delay line is terminated by a multiplexer and a de-multiplexer. A multiple-wavelength buffer can accommodate multiple packets on multiple wavelengths. When the multiple-wavelength buffer is compared with the single-wavelength buffer, the multiple-wavelength buffer requires a larger switch fabric and additional hardware such as multiplexer and demultiplexer. The multiple-wavelength buffer achieves a larger capacity optical buffering on multiple wavelengths. The simulation results in the paper shows far improved performance for the multiple-wavelength delay lines [25].

In contention resolution utilizing wavelength conversion, the signal on each wavelength from the input fiber is first de-multiplexed and sent into the switch. The switch is capable of recognizing the contention and selecting a suitable wavelength converter leading to the desired output fiber. The wavelength converters can convert any incoming wavelength to a fixed desired wavelength or they can convert one or several pre-determined incoming wavelengths to a fixed desired wavelength. The paper reports that the majority of wavelength-conversion techniques demonstrated to date convert to one single wavelength channel. The paper cites a source that reports parametric wavelength conversion is a promising technique offering multichannel wavelength conversion without measurable crosstalk. The paper cites a second source that reports the conversion mechanism can scale well without a large number of wavelength converters by virtue of limited multichannel wavelength conversion [25]. Space deflection is used to resolve packet contention after time and wavelength conversion. Space deflection is carried out in hub nodes. Hub nodes are nodes that have higher nodal degree. The hub nodes will serve as major routing nodes. Individual nodes will have a deflection policy to deflect only to specific nodes. The deflection policy would only be deflected to a node that would eventually lead back to the original next hop [25].

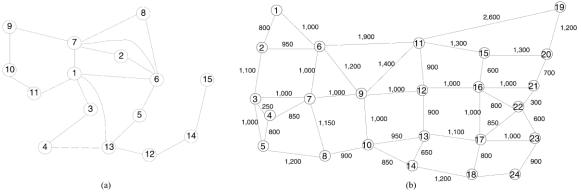

Figure 7 Unified Study's Topology 1 and Topology 2 [25]

Topology 1 and Topology 2 from the Unified Study is shown in Figure 7 above. Topology 1 represents a metro ring network. Topology 2 represents a WAN network. The link length in Topology 1 is 20 km. The link lengths in Topology 2 are shown in Figure 5. Each fiber modeled using 4, 8, and 16 wavelengths. The data rate for each fiber is 2.5 GBPS [25].

The study reports that the main characteristic of internet traffic is its self-similarity. The study also reports that it has been shown in the literature that self-similar traffic can be generated by multiplexing multiple sources of Pareto-distributed ON/OFF periods. The ON period would correspond to back to back packet trains. The OFF periods would be the time

where no packets would be transmitted. The study used a Hurst parameter of ON- and OFFperiod duration distribution of 0.9. Packets arrive without any gap during the ON period [25].

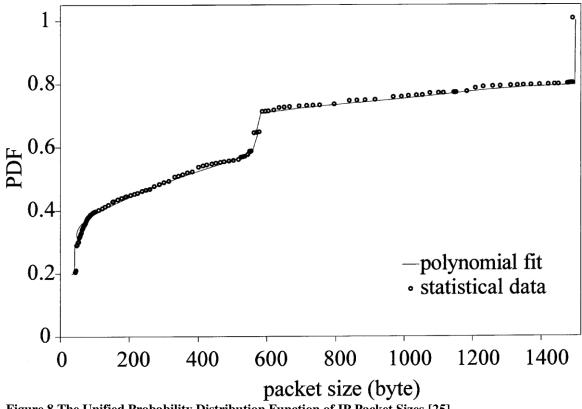

The Unified study used a 19<sup>th</sup> order polynomial to reproduce the IP packet size distribution. The maximum size was set to be 1500 bytes. The probability distribution function was derived from a cited source. The probability function is shown below in Figure 8 [25].

Figure 8 The Unified Probability Distribution Function of IP Packet Sizes [25].

There were three performance metrics chosen to evaluate network performance. The three performance metrics are network throughput, packet loss rate, and average hop distance. The packet loss rate is the total number of dropped packets divided by the total number of packets generated. The network throughput is defined by [25]

Network throughput =

$$\frac{\text{total number of bits successfully delivered}}{(\frac{\text{network transmission capacity x simulation time}}{\text{ideal average hope distance}})$$

Network transmission capacity

= (total # of links) x (# of wavelengths per link) x (data rate)

The Unified study reports that network throughput is the fraction of the network resource that successfully delivers data. The Unified study reports the average hop distance as the hop distance a packet can travel, averaged over all the possible source destination pairs possible. The ideal average hop distance is 2.42 for Topology 1 and 2.99 for Topology 2 [25].

All the results from the Unified study are plotted with offered transmitter load as the abscissa. The offered transmitter load is the total number of bits offered per unit of time divided by the line speed. The average offered link load per wavelength is [25]

Average offered link load =

average offered TX load x total # of TX x average hope distance

# of wavelengths x total number of uni-directtional links

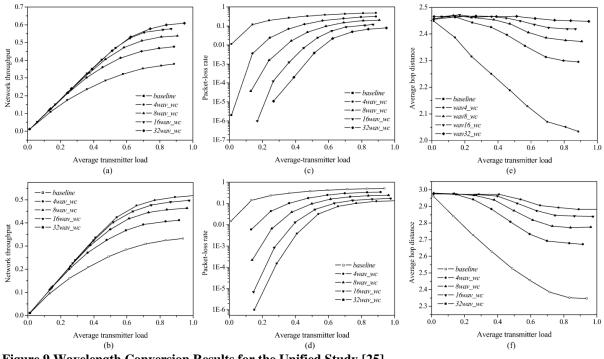

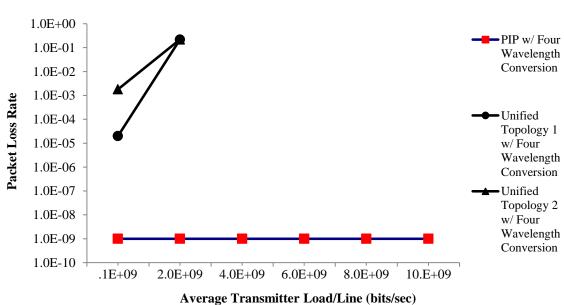

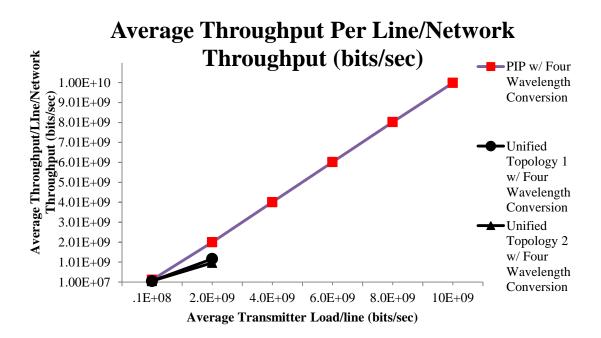

Figure 9 Wavelength Conversion Results for the Unified Study [25]

The wavelength conversion results for the Unified Study are shown above in Figure 9. The average transmitter load is normalized to 2.5 gigabits per second. Figure 9(a) shows the network throughput for wavelength conversion with different number of wavelengths for Topology 1. Figure 9(b) shows the network throughput for wavelength conversion with different number of wavelengths for Topology 2. The network throughput is normalized to 2.5 gigabits per second. Four wavelengths are simulated in baseline without wavelength conversion. The Unified Study reports that more wavelengths provide better throughput

performance. The margin of improvement decreases when the number of wavelengths increases. The network throughput for all architectures is too low. The recommended architectures provide higher throughput with a 10 gigabit per second line [25].

Figure 9(c) and 9(d) compares the packet loss rate for Topology 1 and Topology 2 respectively. Packet loss rates are reduced as the number of wavelengths increases. However, the packet loss rate for all architectures is too high. The recommended architectures in the dissertation provide much lower packet loss rates with a 10 gigabit per second line rate [25].

In the architectures using optical buffering, all the optical delay lines are 1 km in length. This represents a 5 microsecond delay. The delay line is long enough to hold 12000 bits.

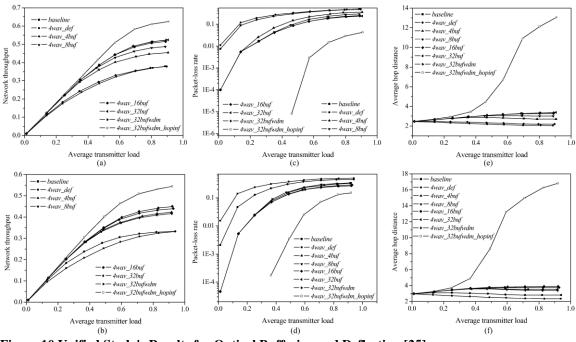

Figure 10 Unified Study's Results for Optical Buffering and Deflection [25]

Figure 10 shows the Unified Study's results for optical buffering and deflection. The average transmitter load is normalized to 2.5 gigabits per second. All architectures have four wavelengths with different buffering and deflection settings. Figure 9(a) compares the network throughput of different optical buffers and deflection architectures for Topology 1. Figure 9(b) compares the network throughput of different optical buffers and deflection architectures and deflection architectures for Topology 2. The network throughput is normalized to 2.5 gigabits per second. Network throughput increases with the number of delay lines. The network throughput saturates after the number of delay lines reaches 16. The maximum hop count limits the number of times a packet can enter a delay line. This effected architectures with 32 delay lines. The maximum hop count was removed in the curves containing hopinf. The network throughput increased considerably in both cases. This improvement was

considerable less than the recommended architectures in the dissertation. The recommended architectures provide higher throughput with a 10 gigabit per second line [25].

Figure 10(c) and 10(d) compares the packet loss rate for Topology 1 and Topology 2 respectively. The average transmitter load is normalized to 2.5 gigabits per second. The Unified study observes that deflection in Topology 2 provides a lower packet loss rate than in Topology 1. The Unified study explains that difference by stating state Topology 2 is a more densely connected network. However, the packet loss rates for all architectures are much higher than the recommended architectures in the dissertation. The recommended architectures in the dissertation. The recommended architectures provide higher throughput with a 10 gigabit per second line rate. The recommended architectures provide higher throughput with a 10 gigabit per second line [25].

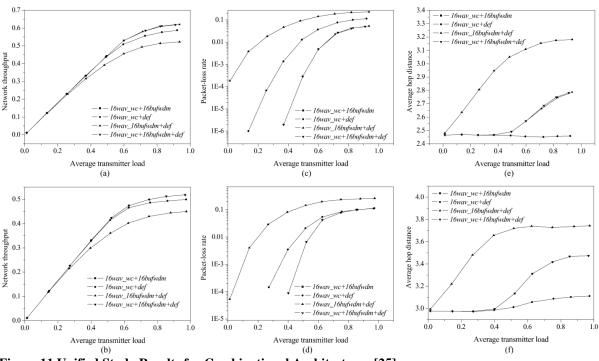

Figure 11 Unified Study Results for Combinational Architectures [25]

Figure 11 shows the Unified Study's results for combinational architectures for wavelength conversion, optical buffering, and deflection. The average transmitter load is normalized to 2.5 gigabits per second. All architectures have sixteen wavelengths with different buffering and deflection settings. Figure 11(a) compares the network throughput of different optical buffers and deflection architectures for Topology 1. Figure 10(b) compares the network throughput of different optical buffers and deflection architectures for Topology 1. Figure 10(b) compares the network throughput of different optical buffers and deflection architectures for Topology 2. The network throughput is normalized to 2.5 gigabits per second. The architecture that uses all three dimensions of wavelength, time, and space has the best network throughput. The Unified Study observes that when wavelength conversion and buffering are used, deflection provides little change in performance. The network throughput for all architectures is too

low. The recommended architectures provide higher throughput with a 10 gigabit per second line [25].

Figure 11(c) and 11(d) compares the packet loss rate for Topology 1 and Topology 2 respectively. The average transmitter load is normalized to 2.5 gigabits per second. The wavelength conversion combined with buffering and deflection provided the best performance. The packet loss rate on the best performer is too high and the network throughput is too low. The recommended architectures in the dissertation provide much lower packet loss rates with a 10 gigabit per second line rate [25].

## 2.1.3.1.2 All-Optical Contention Resolution with Prioritization

The paper entitled, "160 Gb/s All-Optical Contention Resolution with Prioritization using Integrated Photonics Components," presents a method for 160 Gb/s all-optical contention resolution with prioritization using integrated photonic devices. The paper discusses the functional diagram of the all-optical contention resolution method, the experimental set-up, and the results of the experiment [26].

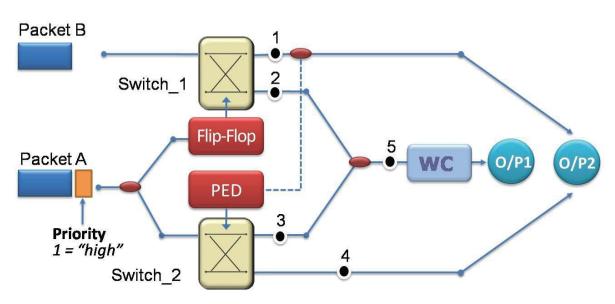

Figure 12 below shows the functional diagram of the optical circuit capable of resolving contention in wavelength and space domain between packets at the same wavelength [26].

Figure 12 Functional Diagram for All-Optical Contention Resolution Method [26]

The functional diagram consists of two 1x2 switches (Switch\_1 and Switch\_2), an Optical Flip-Flop (OFF), a Packet Envelope Detection circuit (PED), and a 160 Gb/s all-optical wavelength converter (WC). Packet A enters the all-optical circuit from input 1. Packet A's priority flag is extracted using narrowband filtering. The extracted label is sent to the Flip-Flop (OFF). This is to generate an optical pulse at  $\lambda_3$  with length slight higher than the data packets. The optical pulse is used to control the state of Switch\_1 and route Packet B. In the presence of  $\lambda_3$ , packet A has priority. Packet B is transmitted from output\_2 of Switch\_1. The packet is then routed to O/P1. O/P1 is a contention port. In the absence of  $\lambda_3$ , packet B is transmitted from output\_1 of Switch\_1 are optically split to the PED. The PED circuit generates packet envelope signals at  $\lambda_4$ . Switch\_2 is controlled by the PED output. Packet A is routed to output\_1 of Switch 2

28

and transmitted to O/P1 when the PED is on. The PED is on when packet B exits and packet A has low priority. If packet A has priority, then it is sent to output\_2 of Switch\_2 and out O/P2. Output\_1 of Switch\_1 and output\_2 of Switch\_2 are combined to the main output port O/P2. Output\_2 of Switch\_1 and output 1 of Switch\_2 are combined to point 5 to resolve contention in the space domain. Packets at point 5 that are wavelength converted to  $\lambda_5$  are represented as contention resolution in the wavelength domain [26].

The experimental setup for the 160 Gb/s all-optical contention resolution is shown below in Figure 13 [26].

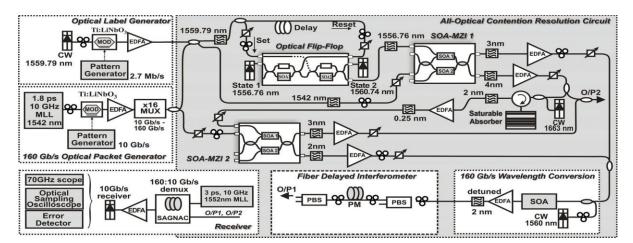

Figure 13 Experimental Setup for 160 Gb/s All-Optical Contention Resolution [26]

A 10 GHz mode-locked laser produced 1.8 picosecond (ps) pulses. The pulses were modulated into data packets containing a  $2^7$ -1 psudorandom binary sequence (PRBS) pattern. The laser generated signal was rate multiplexed to 160 Gb/s in a fiber multiplexer. The laser generated signal produced a sequence of three packets with a 52 ns duration followed by an

empty packet slot. The signal was split in to two parts to create the two incoming packet streams. This is to provide two input streams. The priority flag was added to packet stream A and delayed 90 ns in relation to packet stream B. The priority flag was produced in a second modulator with a1.6 ns duration. Using an optical filter, packet stream A was separated from the priority flag. The extracted priority flag was optically split into two paths with one path being delayed 60 ns. This is to provide the Set and Reset signal to the OFF. The OFF produced 60 ns pulses with 1.4 decibels (db) variation. The optical path of Output\_1 of Switch\_1 led to the PED circuit. The PED circuit consisted of a passive slow absorber-based vertical-cavity semiconductor gate that can be saturated that is powered by a 1564 CW laser. Output\_1 of Switch\_1 and output\_2 of Switch\_2 were time synchronized and combined at the main output port O/P2. Output\_2 of Switch\_1 and output\_1 of Switch\_2 were also time synchronized and combined at the contention port O/P1. The contention output was combined with a 1560 CW laser. The light path circuit was directed on to the SOA and initiating the wavelength conversion. The SOA consists of a 1.1 mm long SOA with a 1.5 nm filter on the end and a delay interferometer. The two 160 Gb/s streams were demultiplexed to 10 Gb/s. The Bit Error Rate (BER) was evaluated for the two 10 Gb/s channels. The results are shown on the next page in Figure 14 [26].

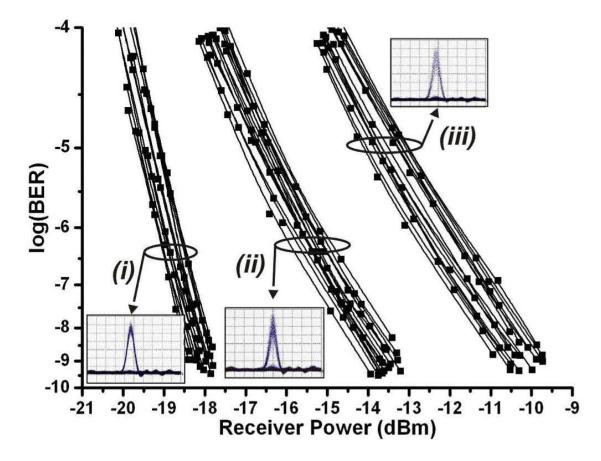

Figure 14 BER Performance for 160 Gbps Contention Resolution Scheme [26]

The contention resolution scheme in [26] provides a much higher line rate than the line rate in the dissertation. However the contention resolution scheme in [26] is limited to two input lines. This will not work in optical networks where there are many input and output lines. The dissertation will work with many input and output lines.

# **Chapter 3 Optical Packet Switch Developed in this Dissertation**

## 3.1 High Level Architecture of a Packet Switch

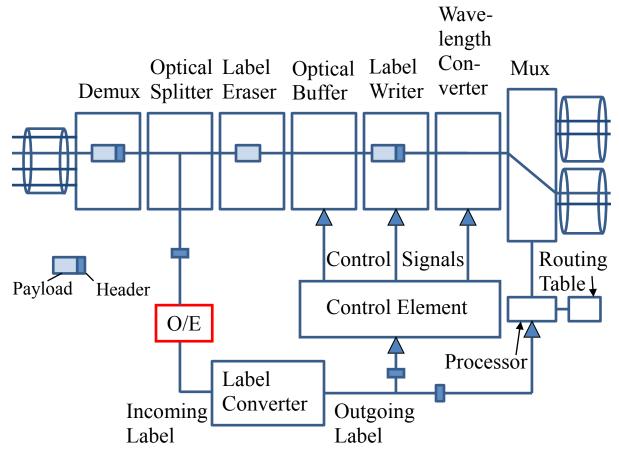

Figure 15 High Level Architecture for Optical Packet Switch [1]

The high level architecture for an optical packet switch is shown above in Figure 12. The high level architecture for an optical packet switch contains components which the optical packet is forwarded. The main components in which the optical packet is forwarded are the demux, the optical splitter, label eraser, optical buffer, wavelength converter, and mux. The packet arrives in the demux. Demux is short for demultiplexer. The packet contains the

header and the payload or body. The header has the packet's label. The body can have either user traffic or control traffic. The demultiplexer separates the wavelengths into separate paths. The optical splitter sends the packet to the control element and the label eraser. The label eraser extracts the header from the packet. The packet is sent to the optical buffer. The body of optical packet remains optical buffer while the packet header is being processed. The header is sent to the optical to electrical converter. The label is converted to electrical information, so the label can be processed electrically. The label is sent to the label converter. The label converter sends the label to the processor. The processor compares the label value to the routing table. Once the next hop is found the new label information is sent is sent to the label converter. The label converter sends the new information to the control element. The control element signals the label writer to write a new label. If the packet needs to be wavelength converted to resolve packet contention, the packet is wavelength converted. The packet is then sent to the mux. Mux is short for multiplexer. The packet is then sent to the requested wavelength and fiber [1].

### **3.2** Current Developments in Enabling Technology for Use in Theses

#### **3.2.1 Larger Optical Memory**

Optical memory is still limited. However optical memory has improved. Reported in [13] is a non-recirculating optical buffer using a crosspoint switch with a total buffer time of 793 nanoseconds. The crosspoint optical switch used in the optical buffer consists of two waveguide layers. At each crosspoint of the switch two active vertical couplers (AVC) are formed by having an active waveguide stacked on top of both input and output passive waveguides. Switching is performed in the crosspoint by using carrier-induced refractive index and gain changes in the AVCs. The crosspoint ON state has the effective refractive index of the active upper layer reduced by the presence of injected carriers to equal that of the lower waveguide thereby allowing coupling. Gain is provided for the signal by the injected carriers in the active layer. This results in a high ON/OFF contrast.

4x4 Crosspoint switch fabrics were demonstrated. The switch fabrics are scalable without the inherent losses associated with broadcast and select schemes. A reference in [13] has shown that the crosspoint switch output power can be dynamically controlled on a packet to packet basis for a large input power range. Another reference in [13] is cited for having optical gain differences of less than 3 decibels (dB) are attainable between the shortest and longest switch paths. A reference in [13] is cited for having attained multicasting without optical split loss. Another reference is cited in [13] that achieves ultra-low OFF state crosstalk in the crosspoint switch by using the highly absorptive state of the active waveguide and the weakened coupling that attenuates the stray signal. The crosstalk is as low as –60 dB has been routinely demonstrated in [13]. The low crosstalk with ultra-fast switching speed, the crosspoint switch provides an excellent electro-optic switch fabric to be used in the implementation of optical packet switches in optical networks.

Additional information on optical delay lines can be found in [14]-[19].

#### **3.2.2 Faster Processing Speed**

A routing lookup system with routing application-specific integrated circuit (ASIC) and offchip routing table for IPv6 is proposed in [20]. The off-chip routing table is a two-level hierarchical memory architecture memory architecture. The off-chip routing table is designed according to the prefix length distribution of 6Net router's routing table. 6Net was a three-year European project to demonstrate continued growth of the internet can be met using IPv6 as the Internet Protocol. The first level of off-chip routing table contains 91.89 percent of routing table entries. The ASIC is made of a content-addressable memory (CAM) and a function unit. The CAM is used as cache memory. The CAM has 1024 entries and guarantees an 80 percent hit ratio by first in first out (FIFO) replacement strategy. The proposed routing system lookup system has table look up rates of 28169 Mlps for IPv6 packet with 128 bit addresses. It is sufficient to satisfy high speed link OC-768 (40 Gbps). The routing table memory size is only 20.04 kilobytes (KB) using ternary contentaddressable memory (TCAM), 10.24 KB using binary content addressable memory (BCAM), and 29.29 KB random access memory (RAM) for 1500 entries. In summary, the CAM with 1024 entries can guarantee an 80 percent hit ratio. The routing lookup speed can approach 213.4 Mlps. The routing lookup speed satisfies the requirement of OC-768 [20].

In [21] an InGaP/GaAs heterojunction bipolar transitor (HBT) integrated circuit implementing a 64-bit programmable look up table (LUT) memory was developed, fabricated and evaluated. In order to demonstrate the high-speed memory application, a

mature and readily available InGaP/GaAs HBT technology was selected. A read function fast enough for a clock rate of 10 GHz was demonstrated by a simulation. An output eye diagram of the memory was generated as simulated at 5 GHz using Cadence's SPECTRE tools and including estimated parasitic capacitances. The circuit model was driven by a pseudo-random source. The circuit model determines a repeating random address set. The memory was synchronously toggled from read and write modes at various times during the transient simulation. Vertical markers on the eye diagram are used to measure the worst-case time delay from the sense amplifier's output to the rowdriver's output. This is the most critical delay path on the chip. The latency during a read cycle is marked with vertical markers on the eye diagram. The worst-case read cycle is 22 picoseconds (ps). The worstcase write cycle is 52 ps. The worst-case read cycle and worst-case write cycle result suggests that the circuit will be able to run in read mode at the target clock frequency of The GaAs HBT integrated circuit was packaged in a 32-pin multi-lead frame 10GHz. package. The 64-bit look up table (LUT) uses 2.0 millimeters (mm) x 2.0 mm of chip area. This includes output buffers but not bondpads. The chip contains approximately 500 transistors, and dissipates approximately 6 Watts (W) at -5.2 volts (V). Functionality of the integrated circuit is demonstrated with a digital test sequence that validates all memory states using an Agilent 16500B mainframe pattern generator and logic analyzer up to 100MHz. A pattern representative of a 27 pseudorandom binary sequence (PRBS) is first written to the memory. After the PRBS is written to memory, the same sequence is read out of the memory. Data in the memory was successfully held over a 30 minute period. A clock rate of 5 GHz was demonstrated experimentally. An Anritsu 12.5Gbps pseudo-random pattern generator source was used in high speed tests. After low-speed programming, a sequence of I's and O's were used to toggle the look up table (LUT) between two memory cells holding different bit values. The results demonstrate successful read operation up to 5GHz. In summary, an InGaP/GaAs HBT implementation of a 64-bit programmable LUT is demonstrated by simulation up to 10GHz and validated experimentally up to 5GHz [21].

### **3.2.3 Numerous Wavelength Division Multiplexing Channels**

Assume many channels. It is possible to have up to 320 channels per fiber. Hence, we can have an available channel all the time. There will be no blockage due to lack of wavelengths [1]-[4].

#### **3.2.4 Network Processors**

Network processors are programmable integrated circuits that perform specific applications. Applications that are typically used by network processors are traffic management, routing, and packet processing. Network processors are found in network routers and switches. Additional information can be found on specific network processors in [22] – [24].

# 3.2.4 Link and Channel Availability Table

| Outgoing Link<br>1 | Channel Type<br>Active<br>Active<br>Active | Channel Number<br>1<br>2<br>3      | Available<br>Yes/No<br>Yes/No<br>Yes/No |

|--------------------|--------------------------------------------|------------------------------------|-----------------------------------------|

|                    | Active<br>Spare<br>Spare                   | N<br>N+1<br>N+2                    | Yes/No<br>Yes/No<br>Yes/No              |

|                    | Spare                                      | M+N                                |                                         |

| Outgoing Link<br>2 | Channel Type<br>Active<br>Active<br>Active | Channel Number<br>1<br>2<br>3      | Available<br>Yes/No<br>Yes/No<br>Yes/No |

|                    | Active<br>Spare<br>Spare<br>Spare          | N<br>N+1<br>N+2<br>N+3             | Yes/No<br>Yes/No<br>Yes/No<br>Yes/No    |

|                    | Spare                                      | N+M                                |                                         |

| Outgoing Link<br>L | Channel Type<br>Active<br>Active<br>Active | :<br>Channel Number<br>1<br>2<br>3 | Available<br>Yes/No<br>Yes/No<br>Yes/No |

|                    | Active                                     | N                                  | Yes/No                                  |

| Spare | N+1 | Yes/No |

|-------|-----|--------|

| Spare | N+2 | Yes/No |

| Spare | N+3 | Yes/No |

|       |     |        |

### Table 1 Link and Channel Availability Table for Outgoing Links

The Link and Channel Availability Channels table is shown on page 33 in Table 1. The table shows the channel availability for each channel on outgoing links. Each outgoing link contains active channels and spare channels. Active channels transmit optical packets where possible and without packet drops. Spare channels transmit packets that would be dropped by the active channels because of packet contention.

Figure 16 Detailed Operational Architecture of Input Side of an Optical Packet Switch

The detailed operational architecture of the input side of an optical packet switch is shown on the previous page in Figure 16. Figure 16 is described in Section 2.1.2.1.

## 3.4 Optical Packet Switch Operational Algorithm at the Switch Input

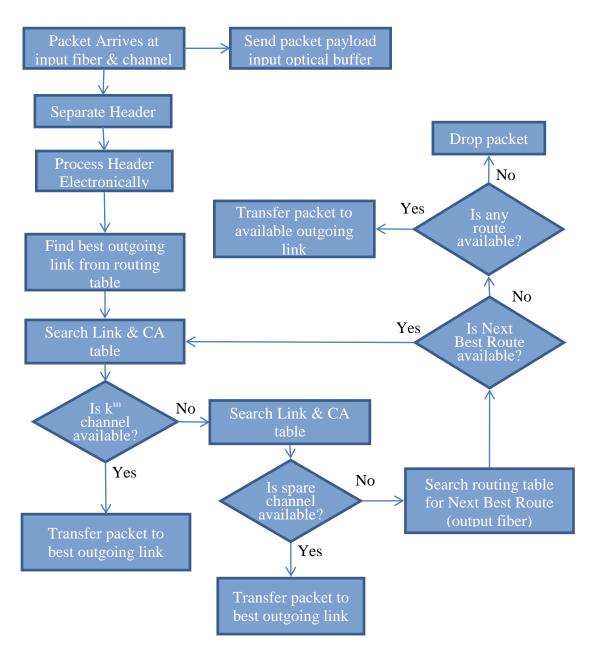

The steps for the optical packet switch operation algorithm at the input side of the optical packet switch are as follows for a packet arriving on the i-th incoming link:

1. The packet header is separated from the body of packet.

2. The main body of packet goes through the input optical buffer.

3. The packet header is processed electronically.

4. The destination node is determined.

5. The best outgoing link for this destination is determined by using the routing table.

6. The channel number k and the corresponding center frequency  $\lambda$  at which the packet arrived is determined.

7. It is determined whether the k-th channel or a spare channel on the best outgoing link is available by using the Link and Channel Availability (CA) Table.

8a. If a channel is available, then transfer the packet to the best outgoing link through the switching fabric using the switch control processor.

8b. If no acceptable channel is available on the best outgoing link then consult routing table and find the Next Best Route for the destination node of the packet and transmit the packet. **3.5** Flow Diagram of Algorithm of Optical Packet Switch Operation at the Switch Input

Figure 17 Flow Diagram of Algorithm of Optical Packet Switch Operation at the Switch Input

The flow diagram of algorithm of optical packet switch operation at the switch input is shown on the previous page in Figure 17.

# **3.6 Optical Packet Switch Operation at the Switch Output**

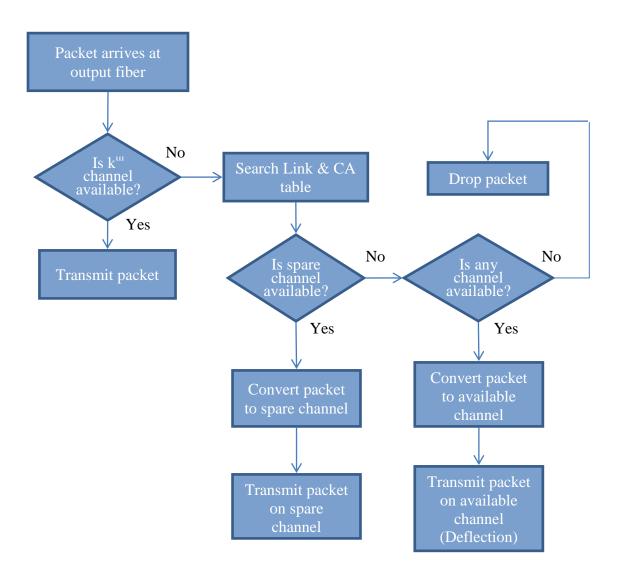

The steps for the optical packet switch operation at the output of the switch are as follows:

1. If the k-th channel is available on the outgoing link on which the packet was transferred then transmit the packet.

2. If the k-th channel is not available on the outgoing link to which the packet was transferred, then find a spare channel on this link, convert the wavelength, and transmit the packet on this spare channel.

3. If no next best fiber and channel is available, send the packet on any available fiber and channel (Deflection).

4. If no fiber and channel is available, then drop the packet.

# 3.7 Flow Diagram of Algorithm of Optical Packet Switch Operation at the

# **Switch Output**

#### Figure 18 Flow Diagram of Algorithm of Optical Packet Switch

The flow diagram of algorithm of optical packet switch operation at the switch output is

shown above in Figure 18.

## **3.8 Performance Evaluation**

#### **3.8.1 Introduction**

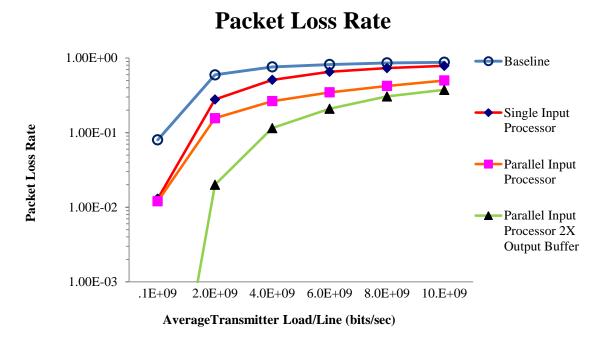

The performance is evaluated in terms of packet loss rate, average throughput and total throughput. The Unified Study evaluated performance in terms of packet loss rate and network throughput.

#### **3.8.2 Packet Loss Rate**

The packet-loss rate is the total number of dropped packets divided by the total number of packets received at the switch.

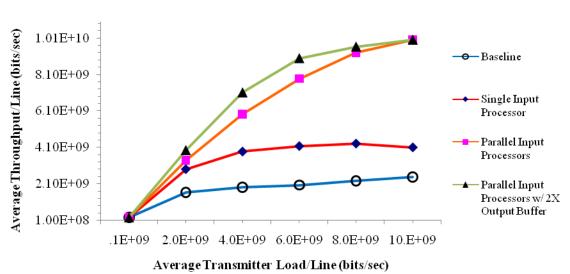

### 3.8.3 Average Throughput per Line

The average throughput per line is the average of each line throughput. The throughput of each line is the average number of bits successfully transmitted by each output buffer per unit time, in bits per second.

Wavelength conversion and Next Best Route (NBR) reduce the average throughput per line. The amount of reduction to the average throughput per line is proportional to the number of lines that are used for wavelength conversion or Next Best Route.

### **3.8.4 Total Throughput**

The total throughput is the sum of each line's average throughput.

## **3.8.5** Network Throughput

Network throughput as defined by [25] is the fraction of the network resource that successfully delivers data. When packets are dropped, a part of the network capacity is not utilized in transferring the bits that are dropped.

Network throughput =

$$\frac{\text{total number of bits successfully delivered}}{\left(\frac{\text{network transmission capacity x simulation time}}{\text{ideal average hope distance}}\right)}$$

Network transmission capacity

= (total # of links) x (# of wavelengths per link) x (data rate)

# **Chapter 4 Simulation Models of the Optical Packet Switch**

A number of architectures were simulated in OPNET Modeler. The list of architectures is

shown below in Table 2.

# 4.1 List of Architectures Modeled, Simulated and Evaluated

| #     | Architectures Scenarios Modeled, Simulated and Evaluated                                 |  |  |

|-------|------------------------------------------------------------------------------------------|--|--|

| 1     | Baseline (Single Input & Output Processor, no wavelength conversion, no Next Best Route) |  |  |

| 2     | Single Input Processor (no contention resolution)                                        |  |  |

| 3     | Single Input Processor with Next Best Route                                              |  |  |

| 4     | Single Input Processor with 4 Wavelength Conversion                                      |  |  |